SERIES

# Analog and Digital Circuits for Electronic Control System Applications

Using the TI MSP430 Microcontroller

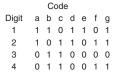

igit 2 Digit 3 b. Segment Codes

TEAM LRN

CO-ROM Included Contains source code and software tools

## Analog and Digital Circuits for Electronic Control System Applications

## Analog and Digital Circuits for Electronic Control System Applications

Using the TI MSP430 Microcontroller

by Jerry Luecke

Newnes is an imprint of Elsevier 200 Wheeler Road, Burlington, MA 01803, USA Linacre House, Jordan Hill, Oxford OX2 8DP, UK

Copyright © 2005, Elsevier Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.com.uk. You may also complete your request on-line via the Elsevier homepage (http://elsevier.com), by selecting "Customer Support" and then "Obtaining Permissions."

Recognizing the importance of preserving what has been written, Elsevier prints its books on acid-free paper whenever possible.

#### Library of Congress Cataloging-in-Publication Data

Luecke, Gerald.

Analog and digital circuits for electronic control system applications : using the TI MSP430 microcontroller / by Gerald Luecke.

p. cm.

ISBN 0-7506-7810-0

1. Electronic circuit design. 2. Electronic control. 3. Programmable controllers. I. Title.

TK7867.L84 2004 629.8'9--dc22

2004054669

#### **British Library Cataloguing-in-Publication Data**

A catalogue record for this book is available from the British Library.

For information on all Newnes publications visit our Web site at www.books.elsevier.com

04 05 06 07 08 09 10 9 8 7 6 5 4 3 2 1

Printed in the United States of America.

The book is dedicated to my wife Velma and our grandchildren:

From the Luecke side: Cameron, Graham, Andy, Alex, Alyssa, Brent, Jacob, Harper, Arielle, Emery.

From the Hubbard side:

Jared, Garrett, Matthew, Ashton, Audrey.

## **Contents**

| Foreword                                             |      |

|------------------------------------------------------|------|

| Preface                                              | xiı  |

| Acknowledgments                                      | xiii |

| What's on the CD-ROM?                                | xiv  |

| Chapter 1: Signal Paths from Analog to Digital       |      |

| Introduction                                         |      |

| A Refresher                                          | 1    |

| Accuracy vs. Speed—Analog and Digital                | 5    |

| Interface Electronics                                |      |

| The Basic Functions for Analog-to-Digital Conversion |      |

| Summary                                              | 8    |

| Chapter 1 Quiz                                       |      |

| Chapter 2: Signal Paths from Digital to Analog       |      |

| Introduction                                         |      |

| The Digital-to-Analog Portion                        |      |

| Filtering                                            |      |

| Conditioning the Signal                              |      |

| Transducing the Signal                               | 13   |

| Summary                                              | 15   |

| Chapter 2 Quiz                                       | 16   |

| Chapter 3: Sensors                                   |      |

| Introduction                                         | 18   |

| Temperature Sensors                                  | 18   |

| Angular and Linear Position                          | 21   |

| Rotation                                             | 24   |

| Magnetoresistor Sensor                               | 24   |

| Pressure                                             | 25   |

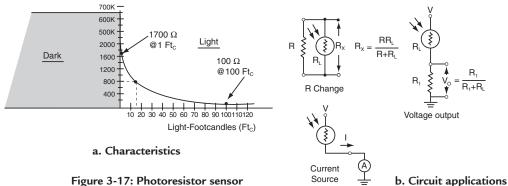

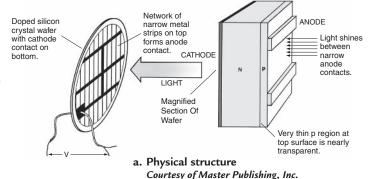

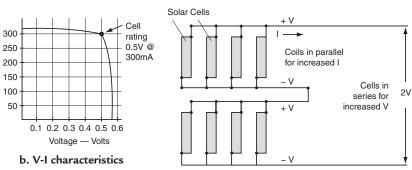

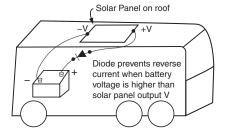

| Light Sensors                                        | 27   |

| Other Sensors                                        | 32   |

| Summary                                              | 32   |

| Chapter 3 Quiz                                       | 32   |

| Chapter 4: Signal Conditioning                       |      |

| Introduction                                         |      |

| Amplification                                        | 35   |

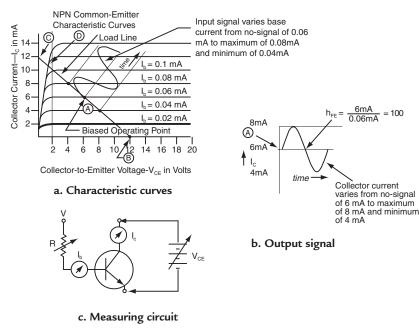

| Bipolar NPN Amplifier                                |      |

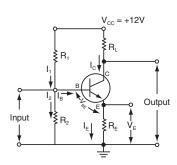

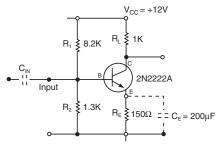

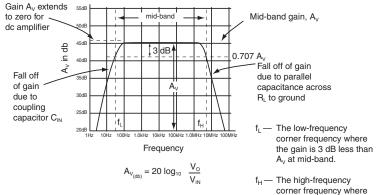

| Amplifier Frequency Response                         | 39   |

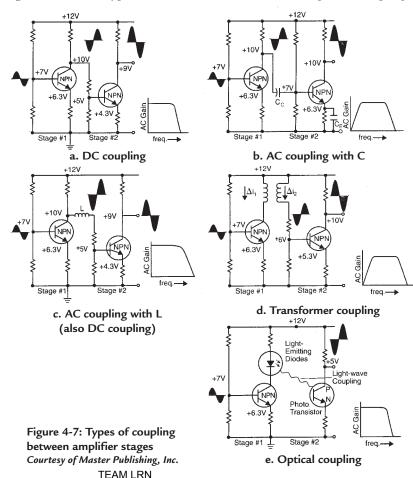

| Coupling                                             | 40   |

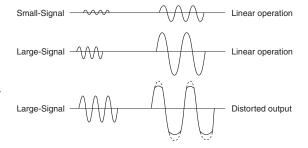

| Small-Signal vs. Large Signal                        |      |

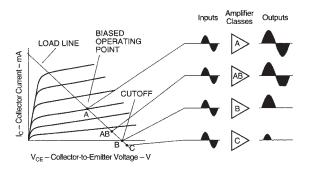

| Classes of Amplifiers                                |      |

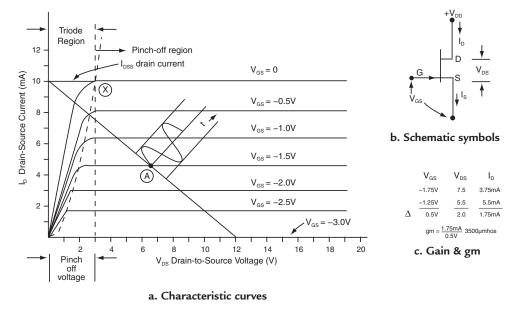

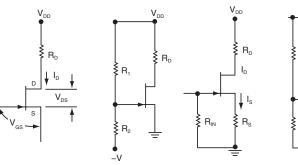

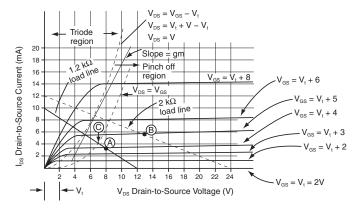

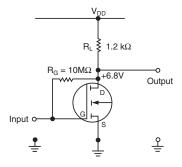

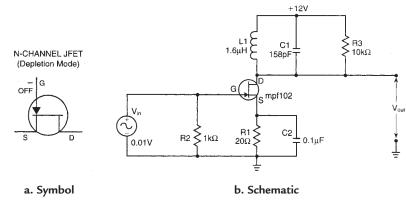

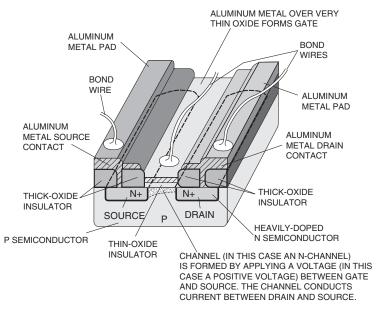

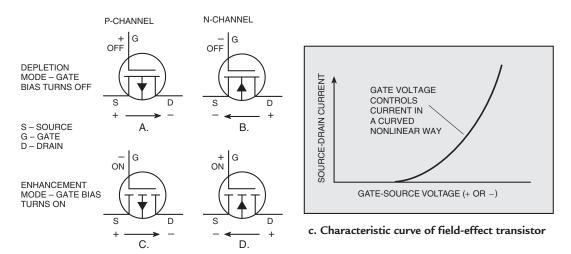

| Field-Effect Transistor Amplifiers                   |      |

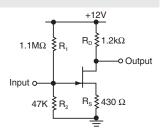

| A N-Channel JFET Amplifier Design                    |      |

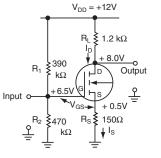

| An NPN MOSFET Amplifier                              | 45   |

#### Contents

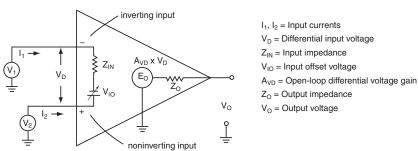

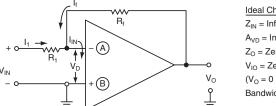

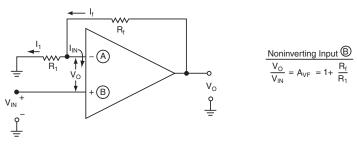

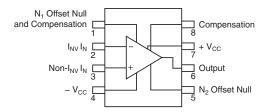

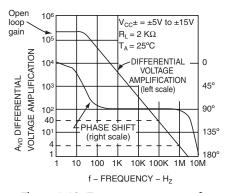

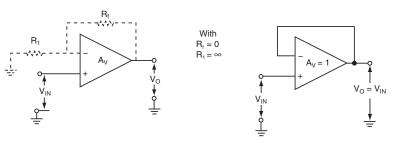

| Operational Amplifiers                                         | 47  |

|----------------------------------------------------------------|-----|

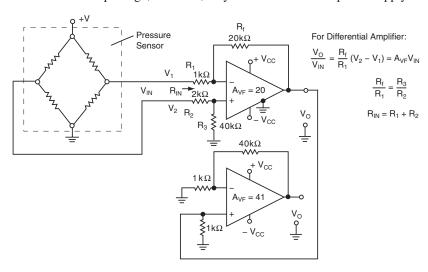

| Conditioning the Output of a Pressure Sensor                   |     |

| A More Sophisticated Pressure Sensor Amplifier                 |     |

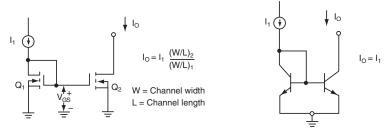

| Current Mirror                                                 |     |

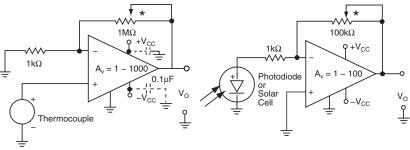

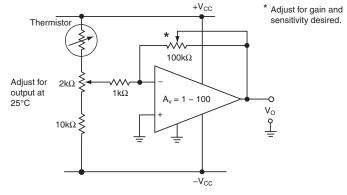

| Applications of Op Amps                                        |     |

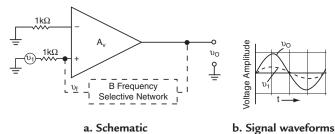

| Oscillators                                                    |     |

| Power Amplifiers                                               |     |

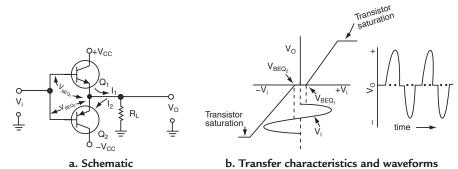

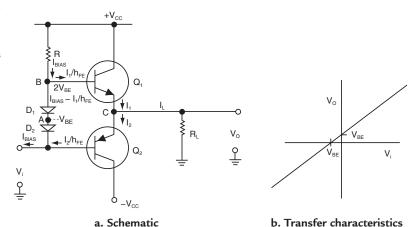

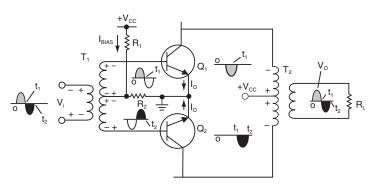

| Class B Audio Power Amplifier                                  |     |

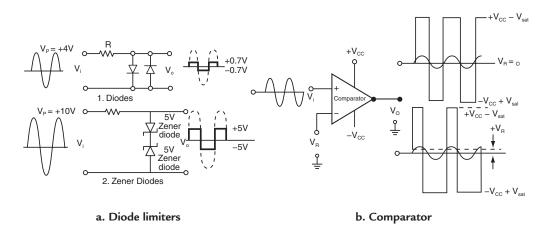

| Special Signals                                                |     |

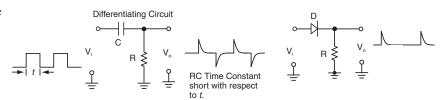

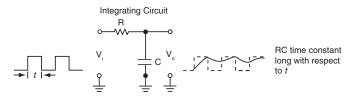

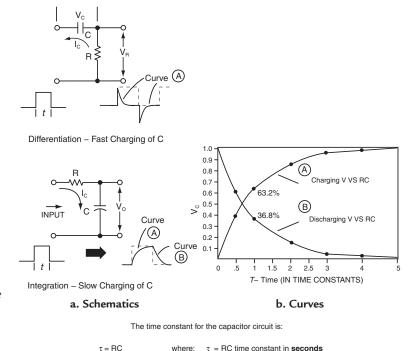

| RC Time Constants                                              |     |

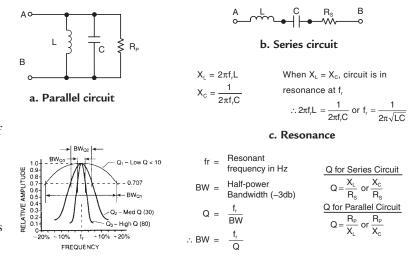

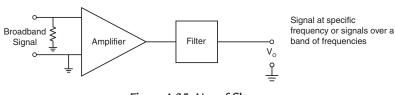

| Frequency Selection                                            |     |

| Typical Application of Filters                                 | 61  |

| Summary                                                        |     |

| Chapter 4 Quiz                                                 | 62  |

| Chapter 5: Analog-to-Digital and Digital-to-Analog Conversions |     |

| Introduction                                                   |     |

| Decimal Equivalent of a Binary Number                          |     |

| Digital Codes of ADC                                           |     |

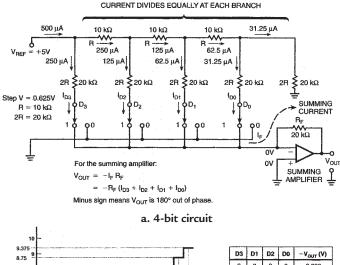

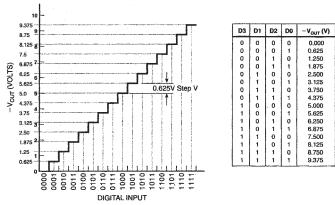

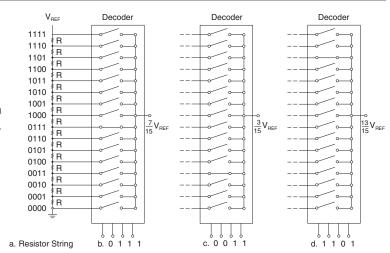

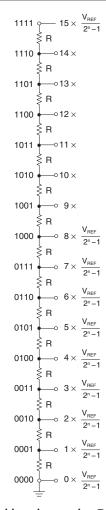

| A Resistor Network DAC                                         |     |

| A Simple Resistor-String DAC                                   |     |

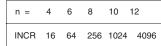

| A Simple Current-Steering DAC                                  |     |

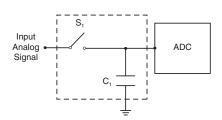

| Analog-to-Digital Converters (ADC)                             |     |

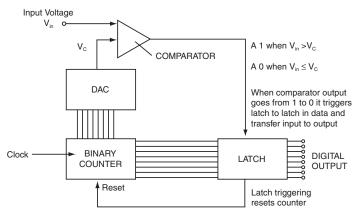

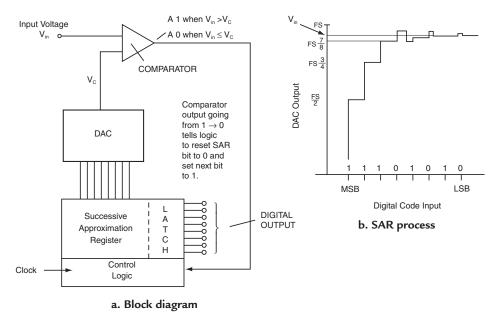

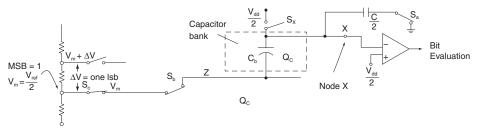

| Successive Approximation Register (SAR) ADC                    |     |

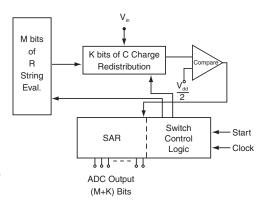

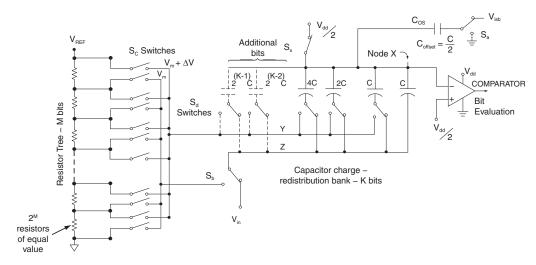

| Capacitor Charge-Redistribution ADC                            |     |

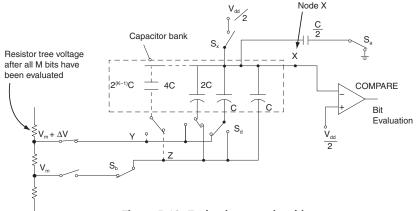

| Highest Speed Conversions                                      | 78  |

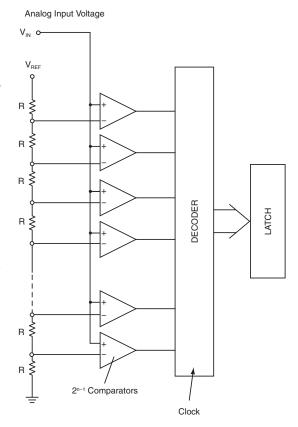

| Sample and Hold and Filters                                    |     |

| Summary                                                        | 79  |

| Chapter 5 Quiz                                                 | 80  |

| Chapter 6: Digital System Processing                           | 82  |

| Introduction                                                   |     |

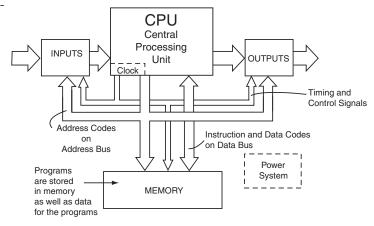

| Digital Processor or Digital Computer                          | 82  |

| What is a Microprocessor?                                      |     |

| What is a Microcomputer?                                       |     |

| System Clarifications                                          | 86  |

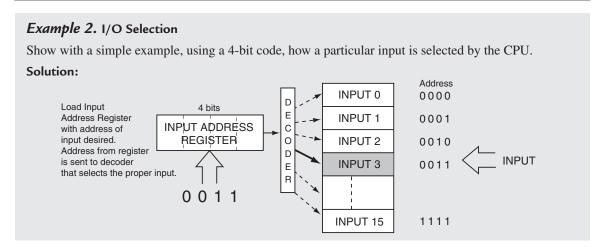

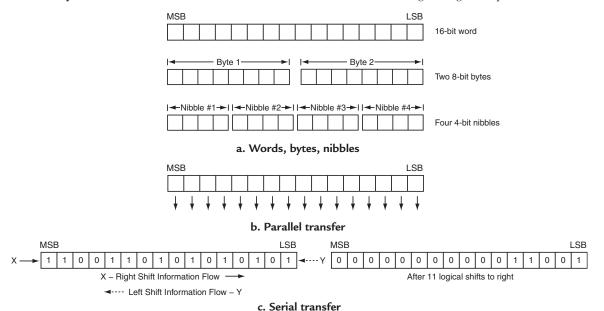

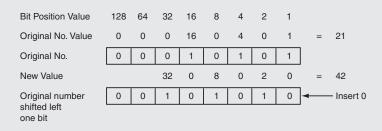

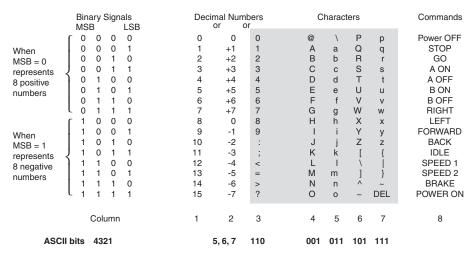

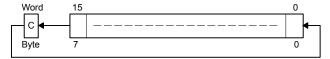

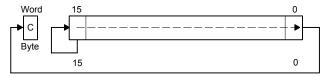

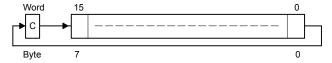

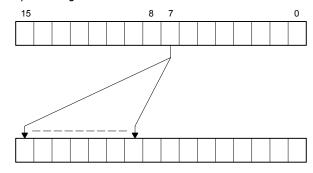

| Digital Signal Representations                                 | 90  |

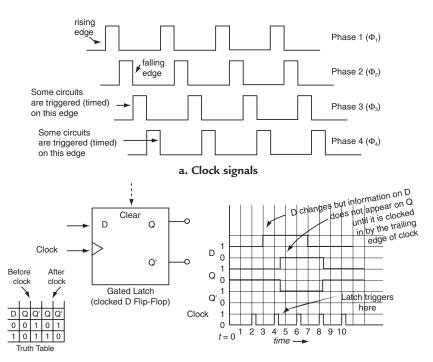

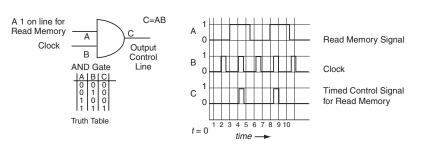

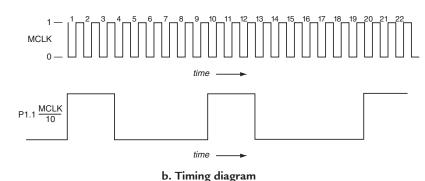

| Clock, Timing and Control Signals                              |     |

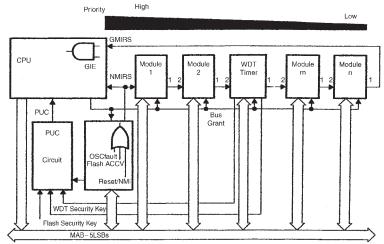

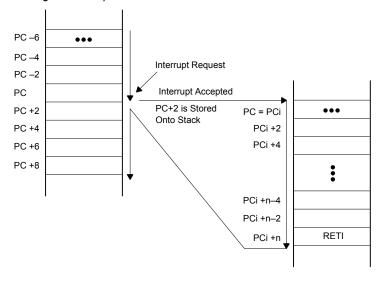

| Interrupts                                                     | 92  |

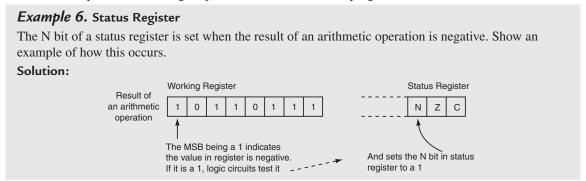

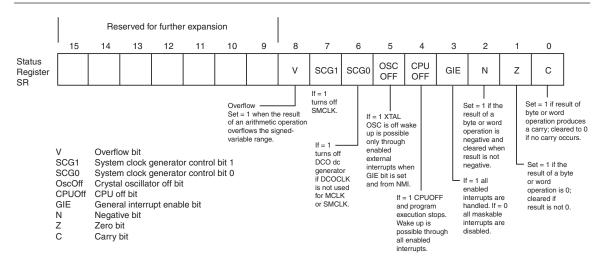

| Status Bits                                                    | 92  |

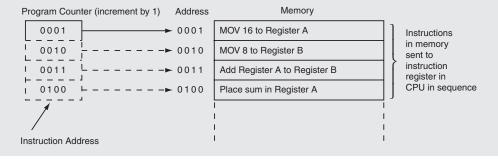

| More About Software                                            | 93  |

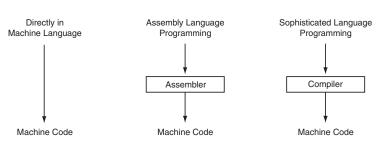

| Sophisticated Programming Languages                            | 95  |

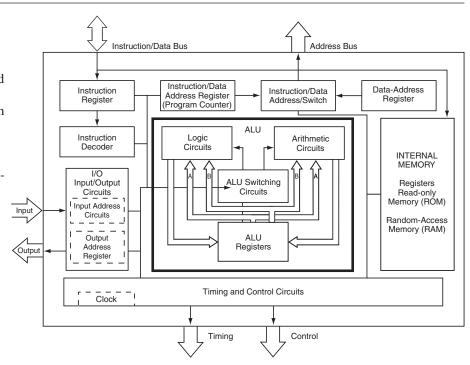

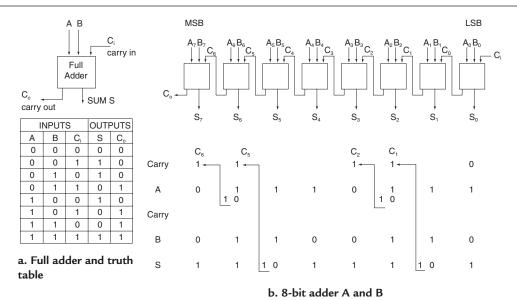

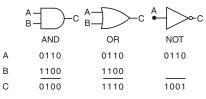

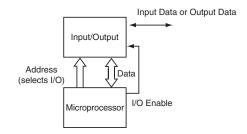

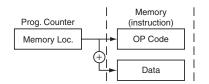

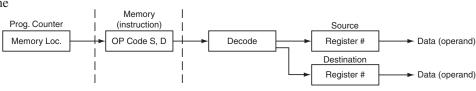

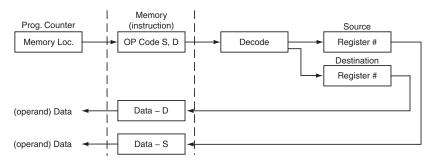

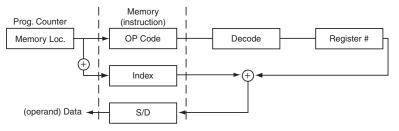

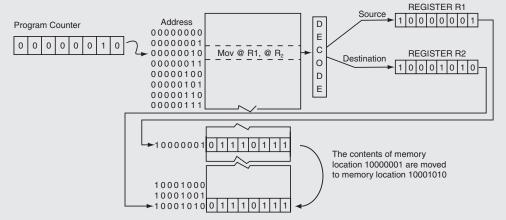

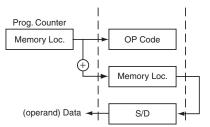

| How Parts of a Processor Perform Their Functions               | 95  |

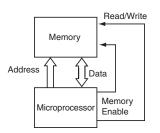

| Memory and Input/Output                                        | 97  |

| Addressing Modes                                               | 97  |

| Summary                                                        | 99  |

| Chapter 6 Quiz                                                 |     |

| Chapter 7: Examples of Assembly-Language Programming           |     |

| Introduction                                                   |     |

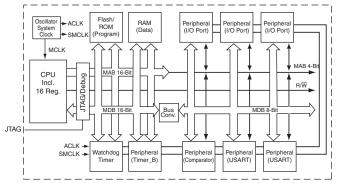

| A Processor for the Examples                                   | 103 |

| About the MSP430 Family                                        | 103 |

| The CPU                                                        | 104 |

| Program Memory and Data Memory          | 105 |

|-----------------------------------------|-----|

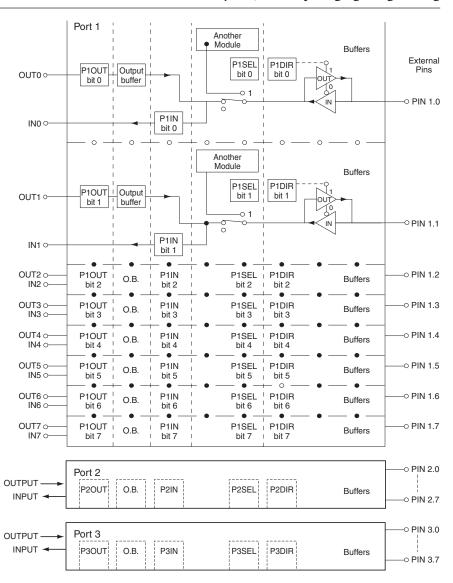

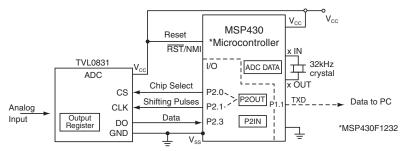

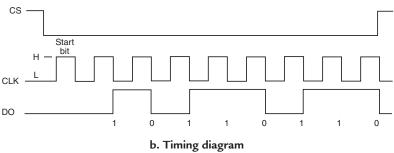

| Peripherals                             |     |

| Operation Control and Operating Modes   |     |

| Watchdog Timer                          |     |

| System Reset                            |     |

| Interrupts                              |     |

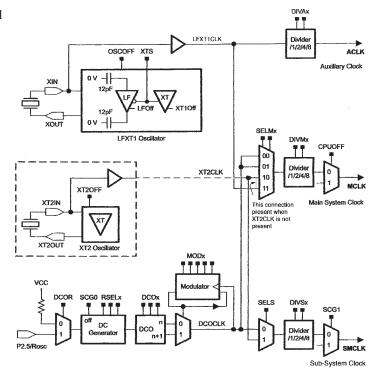

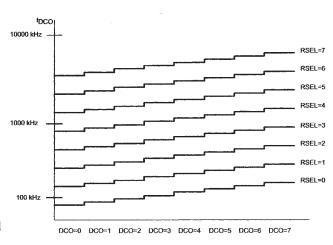

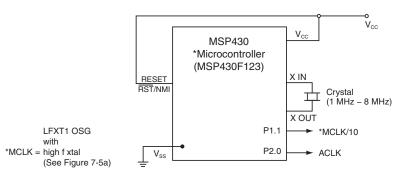

| Oscillators and Clock Generators        |     |

| Timers                                  |     |

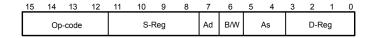

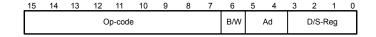

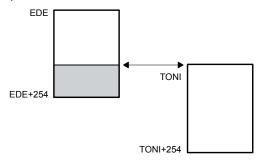

| Addressing Modes                        |     |

| More on MSP430 Control                  |     |

| Further Thoughts                        |     |

| Labels                                  |     |

| Instructions                            |     |

| Operands                                | 117 |

| Hexadecimal Numbers                     |     |

| Comments                                |     |

| Programming Examples                    |     |

| Subprogram No. 1                        |     |

| Subprogram No. 2                        |     |

| Subprogram No. 3                        |     |

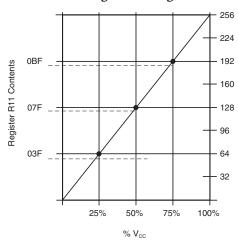

| Variation of Threshold                  |     |

| Summary                                 |     |

| Chapter 7 Quiz                          |     |

| Chapter 8: Data Communications          |     |

| Introduction                            |     |

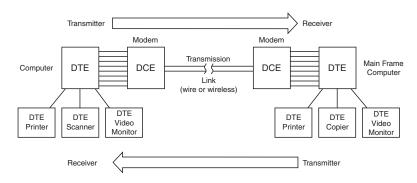

| The Data Transmission System            |     |

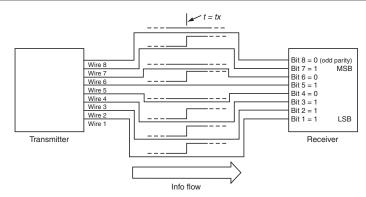

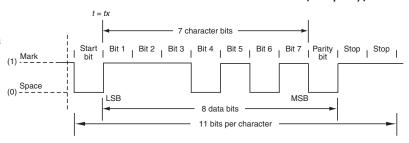

| Parallel and Serial Transmission        |     |

| Protocols                               |     |

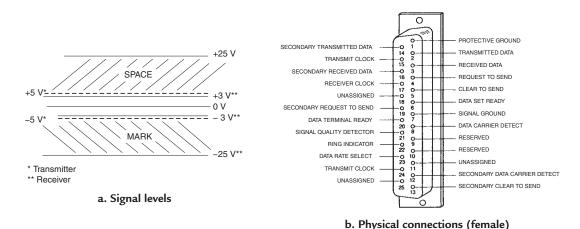

| High-Speed Data Transmissions           |     |

| Serial Data Communications Advances     |     |

| A Return to the Format                  | 145 |

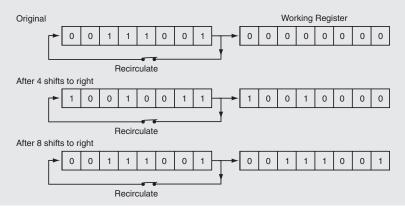

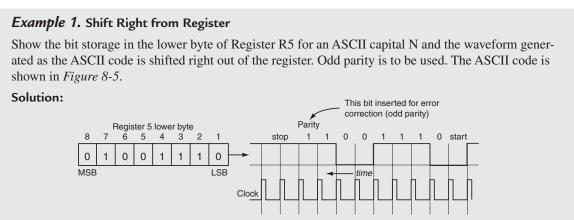

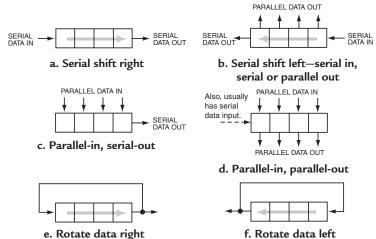

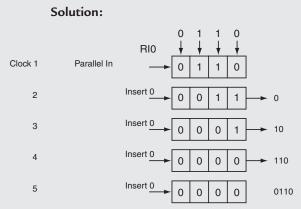

| Shift Registers                         |     |

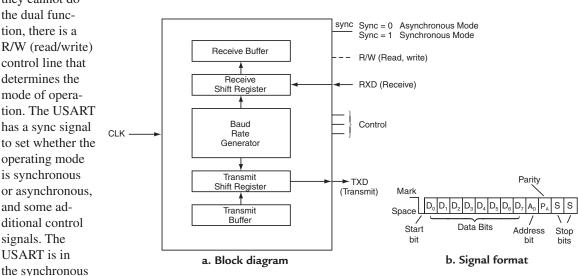

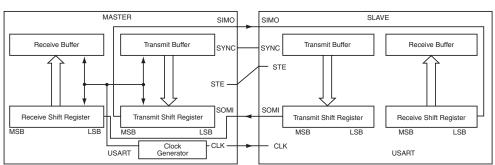

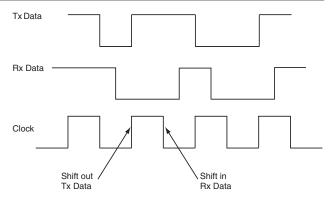

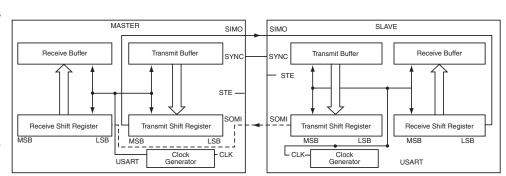

| USART Serial Communications             |     |

| The UART Function with Software.        |     |

| Technology Advances                     |     |

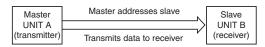

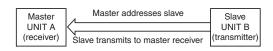

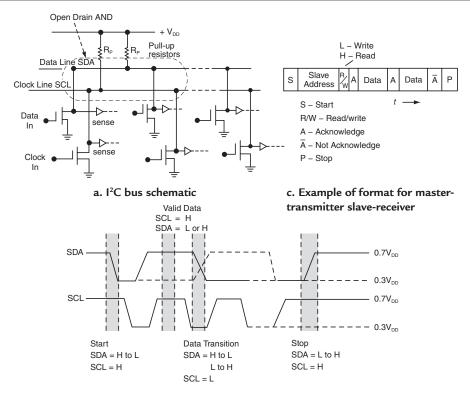

| I <sup>2</sup> C Protocol               |     |

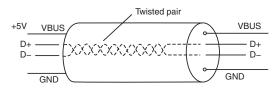

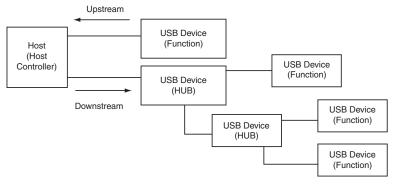

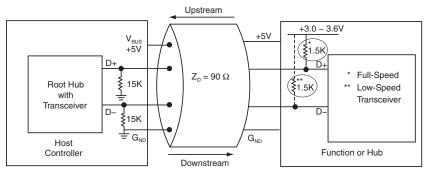

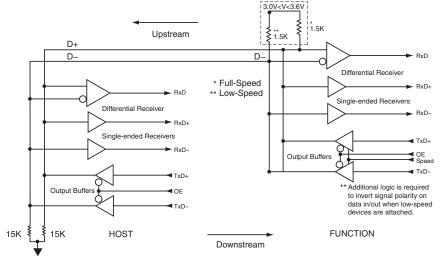

| USB                                     | 152 |

| Summary                                 | 156 |

| Chapter 8 Quiz                          |     |

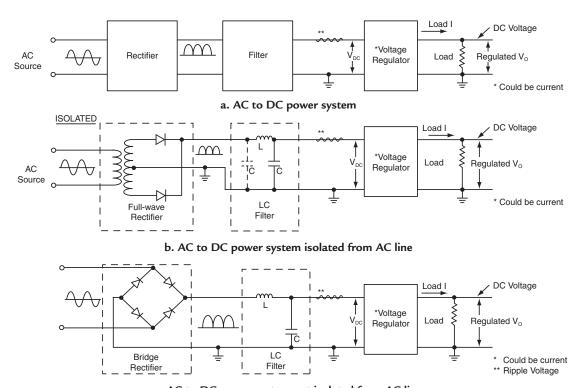

| Chapter 9: System Power and Control     |     |

| Introduction                            |     |

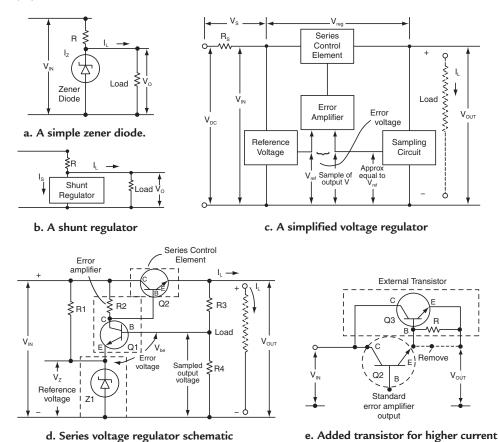

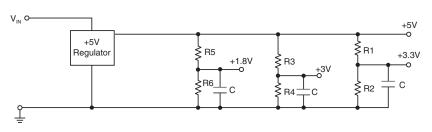

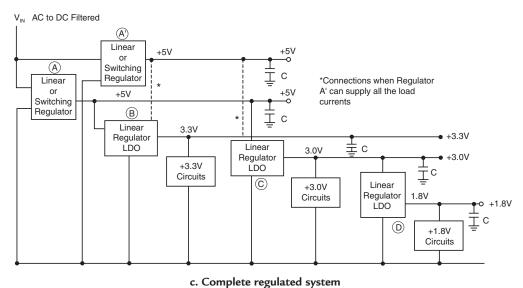

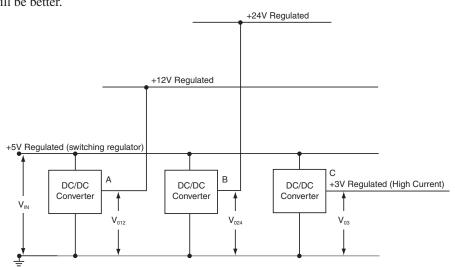

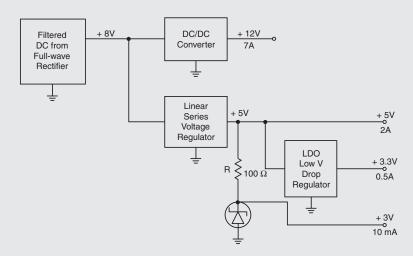

| Voltage Regulators                      |     |

| Load Variations                         |     |

| Actual Linear Voltage Regulator Circuit |     |

| Voltage Regulation                      |     |

| Power Dissipation                       |     |

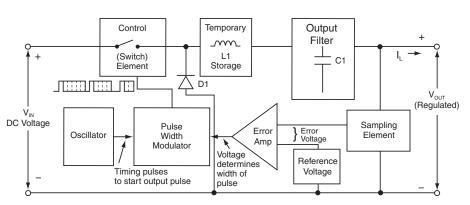

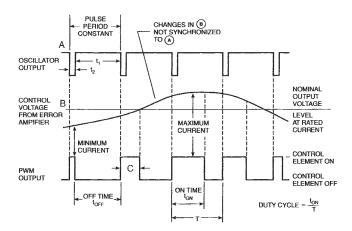

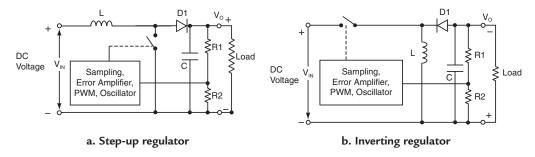

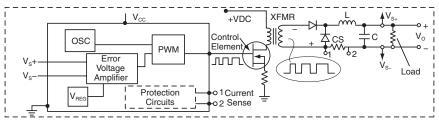

| Switching Voltage Regulators            |     |

| Summary of Regulators                   |     |

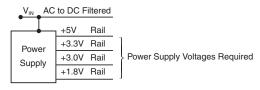

| Power Supply Distribution               |     |

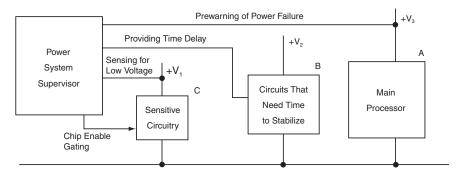

| Power System Supervisors                | 170 |

#### Contents

| Summary                                                                           | 171 |

|-----------------------------------------------------------------------------------|-----|

| Chapter 9 Quiz                                                                    | 171 |

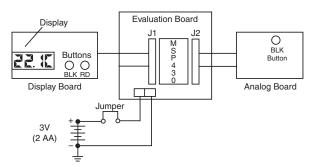

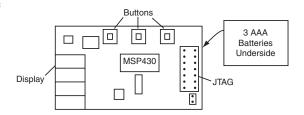

| Chapter 10: A Microcontroller Application                                         | 174 |

| Introduction                                                                      |     |

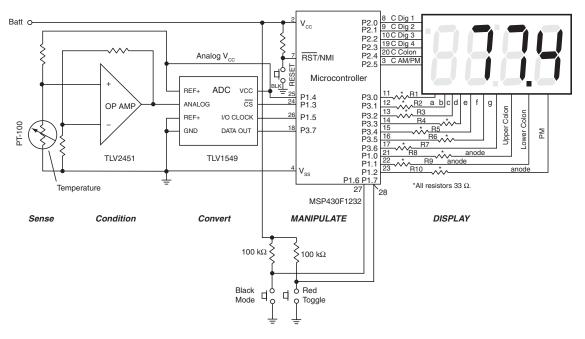

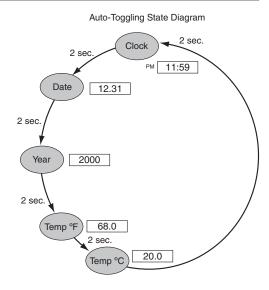

| Application Block Diagram                                                         |     |

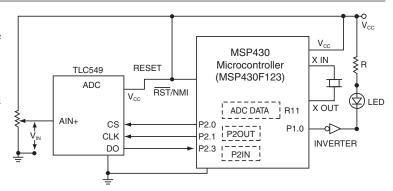

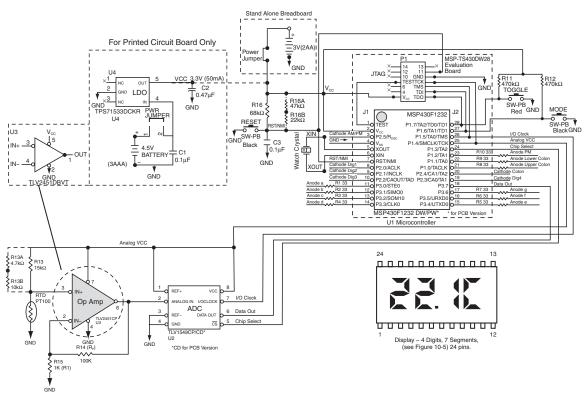

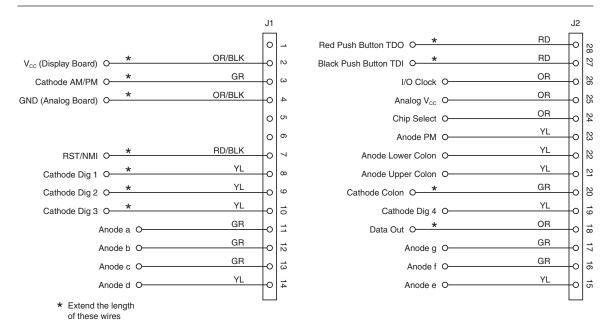

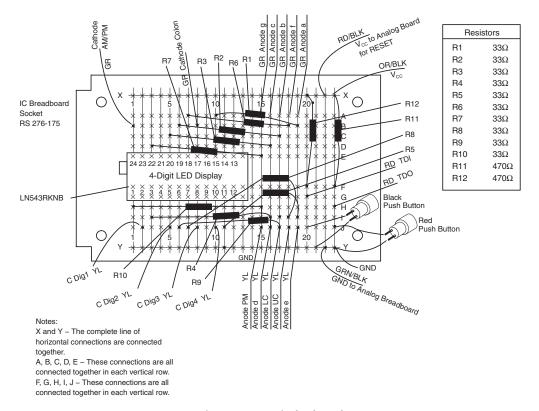

| System Schematic                                                                  | 177 |

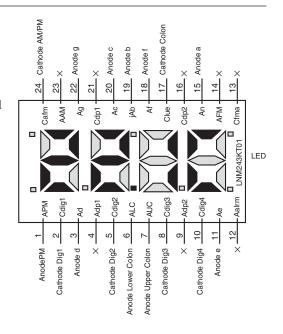

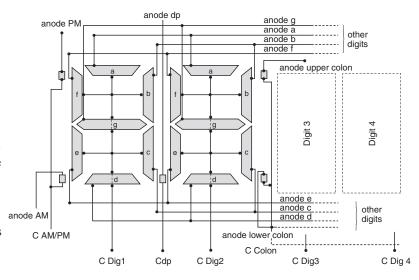

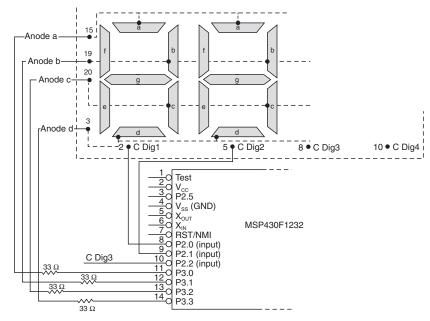

| The Display                                                                       | 177 |

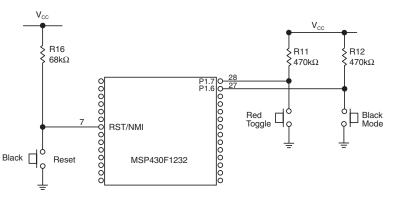

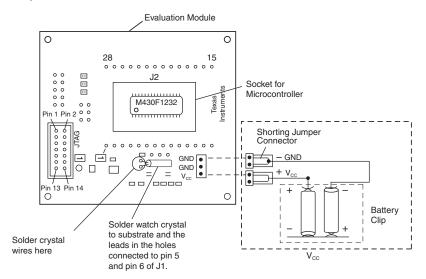

| The Microcontroller                                                               | 179 |

| The Analog Circuitry                                                              | 180 |

| JTAG                                                                              | 181 |

| Summary of Schematic                                                              | 182 |

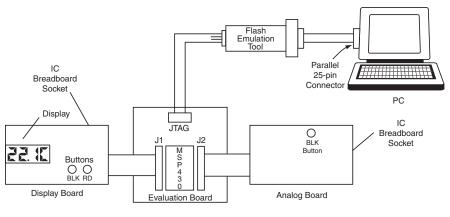

| System Development                                                                | 182 |

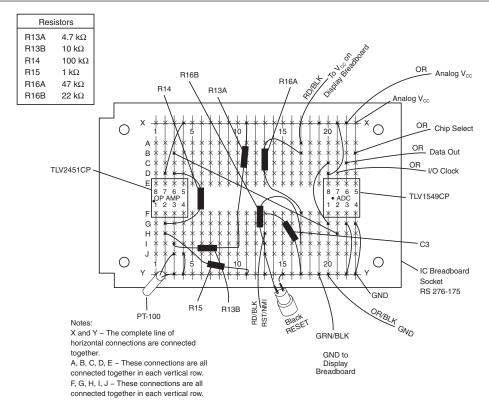

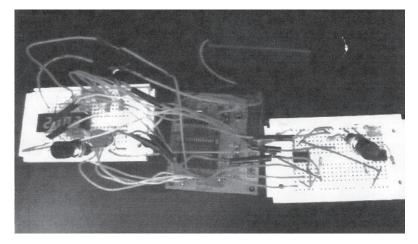

| Breadboard Construction—Powered by the PC                                         |     |

| The Display Board                                                                 | 189 |

| The Analog Board                                                                  | 190 |

| The Application Program                                                           | 191 |

| Creating a Project in IAR Workbench©                                              | 192 |

| Compiling the Program                                                             | 193 |

| Loading the Program                                                               | 194 |

| Troubleshooting                                                                   | 194 |

| The Stand-Alone Breadboard                                                        | 194 |

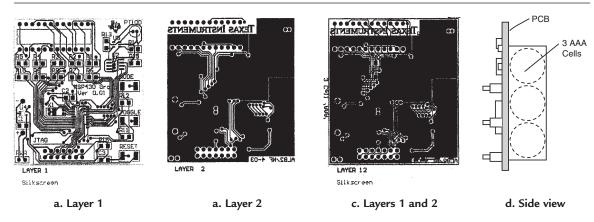

| The PCB Circuit                                                                   | 195 |

| Summary                                                                           | 197 |

| Chapter 10 Quiz                                                                   | 197 |

| Appendix A: The MSP430 Instruction Set                                            | 200 |

| Appendix B: Standard Register and Bit Definitions for the MSP430 Microcontrollers |     |

| Appendix C: Application Program for Use in Chapter 10                             |     |

| Appendix D: A Refresher                                                           |     |

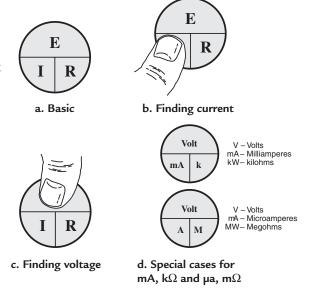

| Ohm's Law                                                                         |     |

| Decibel—A Quantity to Describe Gain                                               |     |

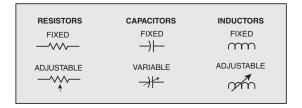

| Passive Devices                                                                   |     |

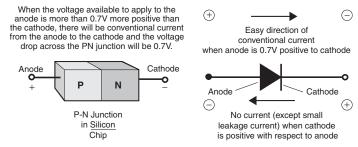

| The Diode—A One-Way Valve for Current                                             |     |

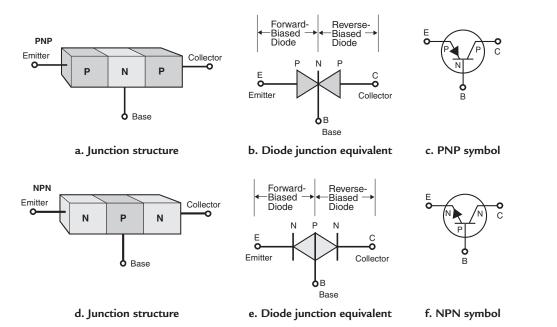

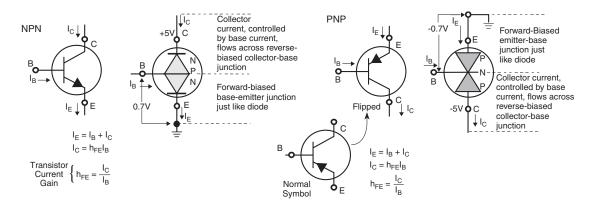

| Active Devices                                                                    |     |

| Four Common Types.                                                                |     |

| About the Author                                                                  |     |

| Inday                                                                             | 200 |

### **Foreword**

#### February 2004

The concept of a programmable system-on-chip (SoC) started in 1972 with the advent of the unassuming 4-bit TMS1000 microcomputer—the perfect fit for applications such as calculators and microwave ovens that required a device with everything needed to embed electronic intelligence. Microcomputers changed the way engineers approached equipment design; for the first time they could reuse proven electronics hardware, needing only to create software specific to the application. The result of microcomputer-based designs has been a reduction in both system cost and time-to-market.

More than thirty years later many things have changed, but many things remain the same. The term microcomputer has been replaced with microcontroller unit (MCU)—a name more descriptive of a typical application. Today's MCU, just like yesterday's microcomputer, remains the heart and soul of many systems. But over time the MCU has placed more emphasis on providing a higher level of integration and control processing and less on sheer computing power. The race for embedded computing power has been won by the dedicated digital signal processor (DSP), a widely used invention of the '80s that now dominates high-volume, computing-intensive embedded applications such as the cellular telephone. But the design engineer's most used tool, when it comes to implementing cost effective system integration, remains the MCU. The MCU allows just the right amount of intelligent control for a wide variety of applications.

Today there are hundreds of MCUs readily available, from low-end 4-bit devices like those found in a simple wristwatch, to high-end 64-bit devices. But the workhorses of the industry are still the versatile 8/16-bit architectures. Choices are available with 8 to 100+ pins and program memory ranging from <1 KB to >64 KB. The MCU's adoption of mixed-signal peripherals is an area that has greatly expanded, recently enabling many new SoC solutions. It is common today to find MCUs with 12-bit analog-to-digital and digital-to-analog converters combined with amplifiers and power management, all on the same chip in the same device. This class of device offers a complete signal-chain on a chip for applications ranging from energy meters to personal medical devices.

Modern MCUs combine mixed-signal integration with instantly programmable Flash memory and embedded emulation. In the hands of a savvy engineer, a unique MCU solution can be developed in just days or weeks compared to what used to take months or years. You can find MCUs everywhere you look from the watch on your wrist to the cooking appliances in your home to the car you drive. An estimated 20 million MCUs ship every day, with growth forecast for at least a decade to come. The march of increasing silicon integration will continue offering an even greater variety of available solutions—but it is the engineer's creativity that will continue to set apart particular system solutions.

Mark E. Buccini Director of Marketing MSP430 Texas Instruments Incorporated

## Preface

Analog system designers many times in the past avoided the use of electronics for their system functions because electronic circuits could not provide the dynamic range of the signal without severe nonlinearity, or because the circuits drifted or became unstable with temperature, or because the computations using analog signals were quite inaccurate. As a result, the design shifted to other disciplines, for example, mechanical.

Today, young engineers requested by their superiors to design an analog control system, have an entirely new technique available to them to help them design the system and overcome the "old" problems. The design technique is this: sense the analog signals and convert them to electrical signals; condition the signals so they are in a range of inputs to assure accurate processing; convert the analog signals to digital; make the necessary computations using the very high-speed IC digital processors available with their high accuracy; convert the digital signals back to analog signals; and output the analog signals to perform the task at hand.

Analog and Digital Circuits for Control System Applications: Using the TI MSP430 Microcontroller explains the functions that are in the signal chain, and explains how to design electronic circuits to perform the functions. Included in this book is a chapter on the different types of sensors and their outputs. There is a chapter on the different techniques of conditioning the sensor signals, especially amplifiers and op amps. There are techniques and circuits for analog-to-digital and digital-to-analog conversions, and an explanation of what a digital processor is and how it works. There is a chapter on data transmissions and one on power control.

And to solidify the learning and applications, there is a chapter that explains assembly-language programming, and also a chapter where the reader actually builds a working project. These two chapters required choosing a digital processor. The TI MSP430 microcontroller was chosen because of its design, and because it is readily available, it is well supported with design and applications documentation, and it has relatively inexpensive evaluation tools.

The goal of the book is to provide understanding and learning of the new design technique available to analog system designers and the tools available to provide system solutions.

## **Acknowledgments**

Mark Buccini, Product Line Marketing Manager for the MSP430 in the Semiconductor Group for Texas Instruments Incorporated and his staff deserve much credit for the project in Chapter 10, and for the thoroughness and accuracy of the MSP430 information. Special thanks go to Neal Frager, an applications expert, for writing the program for the Chapter 10 project, for designing the PCB breadboard, arranging meetings and for researching many inquiries as the book developed. Others that deserve mention for their assistance: Cornelia Huellstrunk, Byron Alsberg who helped develop the initial schematic, Dale Wellborn, Dan Harmon, Rajen Shah, Zack Albus, Modupe Ajibola, Mike Mitchell for his excellent reviews, and Neal Brenner and for helping clean up the last details. A hearty "Thank You" to all!

## What's on the CD-ROM?

■ A fully searchable eBook version of the text in Adobe PDF format. It includes:

Full text of ten chapters.

Appendix A — The MSP430 Instruction Set.

Appendix B — Standard Register and Bit Definitions for the MSP430 Microcontrollers.

Appendix C — Application Program for Use in Chapter 10.

Appendix D — A Refresher.

- A user's guide to the MSP430x1xx family of microcontrollers.

- Layout wiring of PCB interconnection layers.

## Signal Paths from Analog to Digital

#### Introduction

Designers of analog electronic control systems have continually faced the following obstacles in arriving at a satisfactory design:

- 1. Instability and drift due to temperature variations.

- 2. Dynamic range of signals and nonlinearity when pressing the limits of the range.

- 3. Inaccuracies of computation when using analog quantities.

- 4. Adequate signal frequency range.

Today's designers, however, have a significant alternative offered to them by the advances in integrated circuit technology, especially low-power analog and digital circuits. The alternative new design technique for analog systems is to sense the analog signal, convert it to digital signals, use the speed and accuracy of digital circuits to do the computations, and convert the resultant digital output back to analog signals.

The new design technique requires that the electronic system designer interface between two distinct design worlds. First, between analog and digital systems, and second, between the external human world and the internal electronics world. Various functions are required to make the interface. First, from the human world to the electronics world and back again and, in a similar fashion, from the analog systems to digital systems and back again. *Analog and Digital Circuits for Control System Applications* identifies the electronic functions needed, and describes how electronic circuits are designed and applied to implement the functions, and gives examples of the use of the functions in systems.

#### A Refresher

Since the book deals with the electronic functions and circuits that interface or couple analog-to-digital circuits and systems, or vice versa, a short review is provided so it is clearly understood what analog means and what digital means.

#### Analog

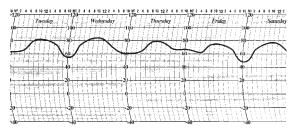

Analog quantities vary continuously, and analog systems represent the analog information using electrical signals that vary smoothly and continuously over a range. A good example of an analog system is the recording thermometer shown in *Figure 1-1*. The actual equipment is shown in *Figure 1-1a*. An ink pen records the

a. Recording thermometer

Photo courtesy of Taylor Precision Products

Plot of daily temperature variations

Courtesy of Master Publishing, Inc.

Figure 1-1: A recording thermometer is an example of an analog system TEAM LRN

temperature in degrees Fahrenheit (°F) and plots it continuously against time on a special graph paper attached to a drum as the drum rotates. The record of the temperature changes is shown in *Figure 1-1b*. Note that the temperature changes smoothly and continuously. There are no abrupt steps or breaks in the data.

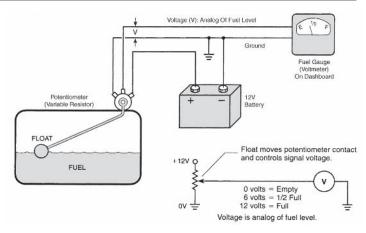

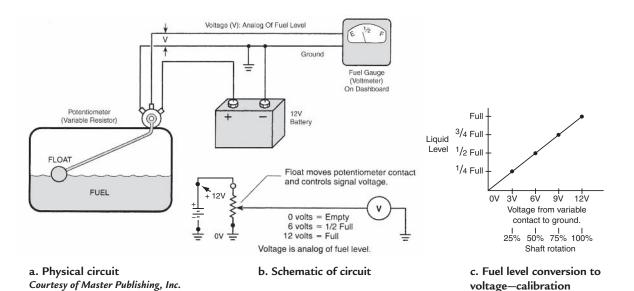

Another example is the automobile fuel gauge system shown in *Figure 1-2*. The electrical circuit consists of a potentiometer, basically a resistor connected across a car battery from the positive terminal to the negative terminal, which is grounded. The resistor has a variable tap that is rotated by a float riding on the surface of the liquid inside the gas tank.

Figure 1-2: The simple circuit for an automobile fuel gauge demonstrates how an electrical quantity, a voltage, is an analog of the fuel level. *Courtesy of Master Publishing, Inc.*

A voltmeter reads the voltage from the variable tap to the negative side of the battery (ground). The voltmeter indicates the information about the amount of fuel in the gas tank. It represents the fuel level in the tank. The greater the fuel level in the tank the greater the voltage reading on the voltmeter. The voltage is said to

be an analog of the fuel level. An analog of the fuel level is said to be a copy of the fuel level in another form—it is *analogous* to the original fuel level. The voltage (fuel level) changes smoothly and continuously so the system is an analog system, but is also an analog system because the system output voltage is a copy of the actual output parameter (fuel level) in another form.

#### Digital

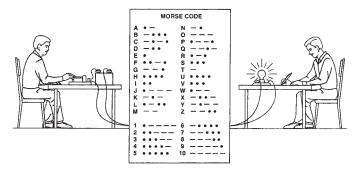

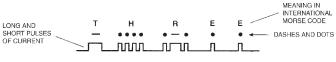

Digital quantities vary in discrete levels. In most cases, the discrete levels are just two values—ON and OFF. Digital systems carry information using combinations of ON-OFF electrical signals that are usually in the form of codes that represent the information. The telegraph system is an example of a digital system.

The system shown in *Figure 1-3* is a simplified version of the original telegraph system, but it will demonstrate the principle and help to define a digital system. The electrical circuit (*Figure 1-3a*) is a battery with a switch in the line at one end and a light bulb at the other. The person

#### a. Electrical circuit

#### b. International Morse code

c. Digital information

Figure 1-3: The telegraph is a digital system that sends information as patterns of switched signals

TEAM LRN

at the switch position is remotely located from the person at the light bulb. The information is transmitted from the person at the switch position to the person at the light bulb by coding the information to be sent using the International Morse telegraph code.

Morse code uses short pulses (dots) and long pulses (dashes) of current to form the code for letters or numbers as shown in *Figure 1-3b*. As shown in *Figure 1-3c*, combining the codes of dots and dashes for the letters and numbers into words sends the information. The sender keeps the same shorter time interval between letters but a longer time interval between words. This allows the receiver to identify that the code sent is a character in a word or the end of a word itself. The T is one dash (one long current pulse). The H is four short dots (four short current pulses). The R is a dot-dash-dot. And the two Es are a dot each. The two states are ON and OFF—current or no current. The person at the light bulb position identifies the code by watching the glow of the light bulb. In the original telegraph, this person listened to a buzzer or "sounder" to identify the code.

Coded patterns of changes from one state to another as time passes carry the information. At any instant of time the signal is either one of two levels. The variations in the signal are always between set discrete levels, but, in addition, a very important component of digital systems is the timing of signals. In many cases, digital signals, either at discrete levels, or changing between discrete levels, must occur precisely at the proper time or the digital system will not work. Timing is maintained in digital systems by circuits called system clocks. This is what identifies a digital signal and the information being processed in a digital system.

#### **Binary**

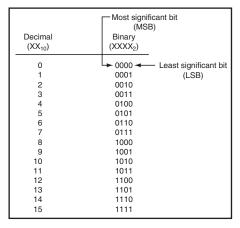

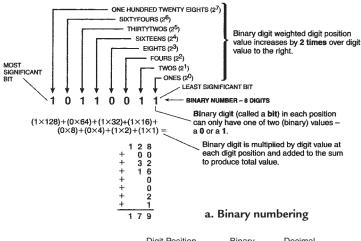

The two levels—ON and OFF—are most commonly identified as 1(one) and zero (0) in modern binary digital systems, and the 1 and 0 are called **bi**nary digits or **bits** for short. Since the system is binary (two levels), the maximum code combinations 2<sup>n</sup> depends on the number of bits, n, used to represent the information. For example, if numbers were the only quantities represented, then the codes would look like *Figure 1-4*, when using a 4-bit code to represent 16 quantities. To represent larger quantities more bits are added. For example, a 16-bit code can represent 65,536 quantities. The first bit at the right edge of the code is called the *least significant bit* (LSB). The left-most bit is called the *most significant bit* (MSB).

#### **Binary Numerical Quantities**

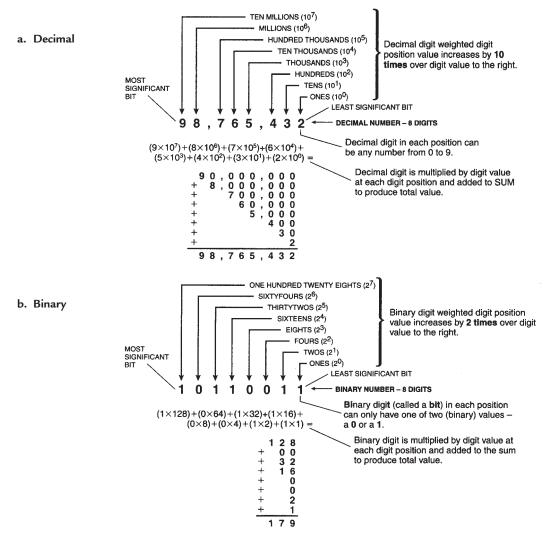

Our normal numbering system is a decimal system. *Figure 1-5* is a summary showing the characteristics of a decimal and a binary numbering system. Note that each system in *Figure 1-5* has

Figure 1-4: 4-bit codes to represent 16 quantities

specific digit positions with specific assigned values to each position. Only eight digits are shown for each system in *Figure 1-5*. Note that in each system, the LSB is either 10<sup>0</sup> in the decimal system or 2<sup>0</sup> in the binary system. Each of these has a value of one since any number to the zero power is equal to one. The following examples will help to solidify the characteristics of the two systems and the conversion between them.

Figure 1-5: Decimal and binary numbering systems Courtesy of Master Publishing, Inc.

#### Example 1. Identifying the Weighted Digit Positions of a Decimal Number

Separate out the weighted digit positions of 6524.

#### Solution:

$$6524 = 6 \times 10^{3} + 5 \times 10^{2} + 2 \times 10^{1} + 4 \times 10^{0}$$

$$6524 = 6 \times 1000 + 5 \times 100 + 2 \times 10 + 4 \times 1$$

6524 = 6000 + 500 + 20 + 4

Can be identified as 6524<sub>10</sub> since decimal is a base 10 system. Normally 10 is omitted since it is understood.

#### Example 2. Converting a Decimal Number to a Binary Number

Convert 103 to a binary number.

#### **Solution:**

$103_{10}/2 = 51$  with a remainder of 1

51/2 = 25 with a remainder of 1

25/2 = 12 with a remainder of 1

12/2 = 6 with a remainder of 0

6/2 = 3 with a remainder of  $\mathbf{0}$

3/2 = 1 with a remainder of 1

1/2 = 0 with a remainder of 1 (MSB)

$103_{10} = 1100111$

#### Example 3. Determining the Decimal Value of a Binary Number

What decimal value is the binary number 1010111?

#### Solution:

Solve this the same as *Example 1*, but use the binary digit weighted position values.

Since this is a 7-bit number:

And since the MSB is a 1, then MSB =  $\mathbf{1} \times 2^6 = 64$ and (next digit)  $\mathbf{0} \times 2^5 = 0$ and (next digit)  $\mathbf{1} \times 2^4 = 16$ and (next digit)  $\mathbf{0} \times 2^3 = 0$

and (next digit)  $0 \times 2 = 0$ and (next digit)  $1 \times 2^2 = 4$ and (next digit)  $1 \times 2^1 = 2$

and (next digit, LSB)  $1 \times 2^0 = \frac{1}{87}$

#### Binary Alphanumeric Quantities

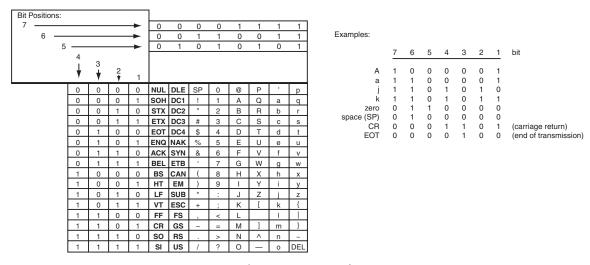

If alphanumeric characters are to be represented, then *Figure 1-6*, the ASCII table defines the codes that are used. For example, it is a 7-bit code, and capital M is represented by 1001101. Bit #1 is the LSB and bit #7 is the MSB. As shown, upper and lower case alphabet, numbers, symbols, and communication codes are represented.

#### Accuracy vs. Speed— Analog and Digital

Quantities in nature and in the human world are typically analog. The temperature, pressure, humidity and wind velocity in our

| Bit F | Posit | ion |   |       |   |     |     |     |   |     |     |     |

|-------|-------|-----|---|-------|---|-----|-----|-----|---|-----|-----|-----|

|       |       |     |   |       | 0 | 1 ( | ) . | 1   | 1 | 0   | 0 - | 1   |

|       |       |     |   |       | 0 | 0   | 1   | 1   | 1 | 1   | 0   | 0   |

| 1     | 2     | 3   | 4 | 5 6 7 | 1 | 1   | 1   | 1   | 0 | 0   | 0   | 0   |

| 0     | 0     | 0   | 0 |       | @ | Р   | '   | р   | 0 | sp  | NUL | DLE |

| 1     | 0     | 0   | 0 |       | Α | Q   | а   | q   | 1 | . ! | SOH | DC1 |

| 0     | 1     | 0   | 0 |       | В | R   | b   | r   | 2 | "   | STX | DC2 |

| 1     | 1     | 0   | 0 |       | С | S   | С   | s   | 3 | #   | ETX | DC3 |

| 0     | 0     | 1   | 0 |       | D | Т   | d   | t   | 4 | \$  | EOT | DC4 |

| 1     | 0     | 1   | 0 |       | Е | U   | е   | u   | 5 | %   | ENQ | NAK |

| 0     | 1     | 1   | 0 |       | F | V   | f   | V   | 6 | &   | ACK | SYN |

| 1     | 1     | 1   | 0 |       | G | W   | g   | w   | 7 | ,   | BEL | ETB |

| 0     | 0     | 0   | 1 |       | Н | Х   | h   | х   | 8 | (   | BS  | CAN |

| 1     | 0     | 0   | 1 |       | Ι | Υ   | i   | у   | 9 | )   | HT  | EM  |

| 0     | 1     | 0   | 1 |       | J | Z   | j   | Z   | : | *   | LF  | SUB |

| 1     | 1     | 0   | 1 |       | K | [   | k   | {   | ; | +   | VT  | ESC |

| 0     | 0     | 1   | 1 |       | L | ١   | - I | I   | < | ,   | FF  | FS  |

| 1     | 0     | 1   | 1 |       | М | ]   | m   | }   | = | -   | CR  | GS  |

| 0     | 1     | 1   | 1 |       | N | ^   | n   | ~   | > |     | SO  | RS  |

| 1     | 1     | 1   | 1 |       | 0 | _   | 0   | DEL | ? | /   | SI  | US  |

Figure 1-6: American Standard Code for Information Interchange—ASCII code TEAM LRN

environment all change smoothly and continuously, and in many cases, slowly. Instruments that measure analog quantities usually have slow response and less than high accuracy. To maintain an accuracy of 0.1% or 1 part in 1000 is difficult with an analog instrument.

Digital quantities, on the other hand, can be maintained at very high accuracy and measured and manipulated at very high speed. The accuracy of the digital signal is in direct relationship to the number of bits used to represent the digital quantity. For example, using 10 bits, an accuracy of 1 part in 1024 is assured. Using 12 bits gives four times the accuracy (1 part in 4096), and using 16 bits gives an accuracy of 0.0015%, or 1 part in 65,536. And this accuracy can be maintained as digital quantities are manipulated and processed very rapidly, millions of times faster than analog signals.

The advent of the integrated circuit has propelled the use of digital systems and digital processing. The small space required to handle a large number of bits at high speed and high accuracy, at a reasonable price, promotes their use for high-speed calculations.

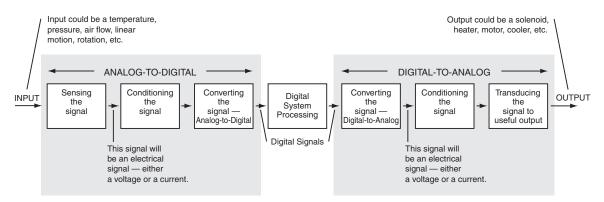

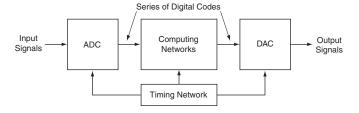

As a result, if analog quantities are required to be processed and manipulated, the new design technique is to first convert the analog quantities to digital quantities, process them in digital form, reconvert the result to analog signals and output them to their destination to accomplish a required task. The complete procedure is indicated in *Figure 1-7*, and the need for analog circuits, digital circuits and the conversion circuits between them is immediately apparent.

Figure 1-7: A typical system describing the functions in the analog-to-digital and digital-to-analog chain

#### Interface Electronics

The system shown in *Figure 1-7* shows the major functions needed to couple analog signals to digital systems that perform calculations, manipulate, and process the digital signals and then return the signals to analog form. This chapter deals with the analog-to-digital portion of *Figure 1-7*, and *Chapter 2* will deal with the digital-to-analog portion.

#### The Basic Functions for Analog-to-Digital Conversion

#### Sensing the Input Signal

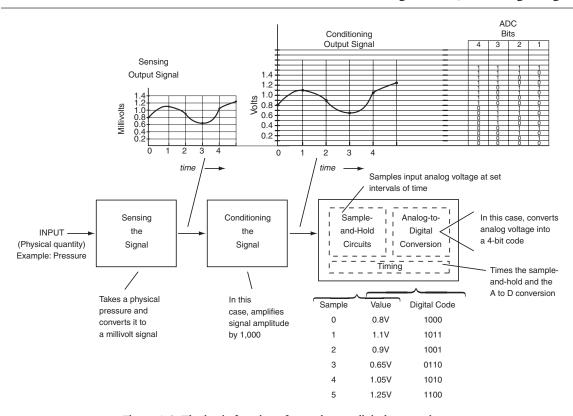

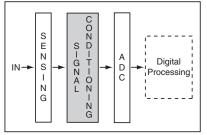

Figure 1-8 separates out the analog-to-digital portion of the Figure 1-7 chain to expand the basic functions in the chain. Most of nature's inputs such as temperature, pressure, humidity, wind velocity, speed, flow rate, linear motion or position are not in a form to input them directly to electronic systems. They must be changed to an electrical quantity—a voltage or a current—in order to interface to electronic circuits.

Figure 1-8: The basic functions for analog-to-digital conversion

The basic function of the first block is called sensing. The components that sense physical quantities and output electrical signals are called sensors.

The sensor illustrated in *Figure 1-8* measures pressure. The output is in millivolts and is an analog of the pressure sensed. An example output plotted against time is shown.

#### Conditioning the Signal

Conditioning the signal means that some characteristic of the signal is being changed. In *Figure 1-8*, the block is an amplifier that increases the amplitude of the signal by 1,000 times so that the output signal is now in volts rather than millivolts. The amplification is linear and the output is an exact reproduction of the input, just changed in amplitude. Other signal conditioning circuits may reduce the signal level, or do a frequency selection (filtering), or perform an impedance conversion. Amplification is a very common signal conditioning function. Some electronic circuits handle only small-signal signals, while others are classified as power amplifiers to supply the energy for outputs that require lots of joules (watts are joules/second).

#### Analog-to-Digital Conversion

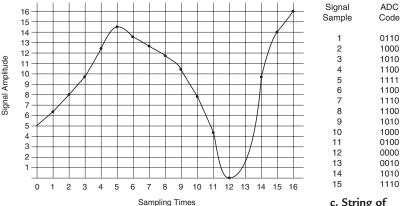

In the basic analog-to-digital conversion function, as shown in *Figure 1-7*, the analog signal must be changed to a digital code so it can be recognized by a digital system that processes the information. Since the analog signal is changing continuously, a basic subfunction is required. It is called a *sample-and-hold* function. Timing circuits (clocks) set the sample interval and the function takes a sample of the input signal and holds on to it. The sample-and-hold value is fed to the analog-to-digital converter that generates a

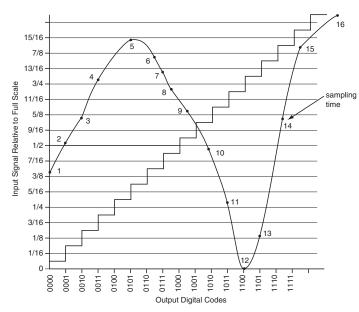

digital code whose value is equivalent to the sample-and-hold value. This is illustrated in *Figure 1-8* as the conditioned output signal is sampled at intervals 0, 1, 2, 3, and 4 and converted to the 4-bit codes shown. Because the analog signal changes continually, there maybe an error between the true input voltage and the voltage recorded at the next sample.

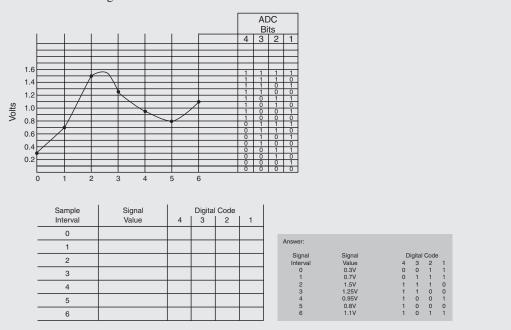

#### Example 4. A to D Conversion

For the analog signal shown in the plot of voltage against time and the 4-bit codes given for the indicated analog voltages, identify the analog voltage values at the sample points and the resultant digital codes and fill in the following table.

Obviously, one would like to increase the sampling rate to reduce this error. However, depending on the code conversion time, if the sample rate gets to large, there is not enough time for the conversion to be completed and the conversion function fails. Thus, there is a compromise in the analog-to-digital converter between the speed of the conversion process and the sampling rate. Output signal accuracy also plays a part. If the output requires more bits to be able to represent the magnitude and the accuracy required, then higher-speed conversion circuits and more of them are going to be required. Thus, design time, cost, and all the design guidelines enter in. *Chapter 5* is a complete chapter on the conversion techniques to explore this function in detail. As shown in *Figure 1-8*, the bits of the digital code are presented all at the same time (in parallel) at each sample point. Other converters may present the codes in a serial string. It depends on the conversion design and the application.

#### Summary

This chapter reviewed analog and digital signals and systems, digital codes, the decimal and binary number systems, and the basic functions required to convert analog signals to digital signals. The next chapter will complete the look at the basic functions required to convert digital signals to analog signals. It will be important to have these basic functions in mind as the electronic circuits that perform these functions are discussed in the upcoming chapters.

#### Chapter 1 Quiz

- 1. A new design technique available to analog system designers is:

- a. Sense the analog, compute using analog, output analog.

- b. Sense the analog, convert to digital, compute digitally, convert to analog, output analog.

- c. Sense the analog, convert to digital, compute digitally, output digitally.

- d. Sense digitally, compute digitally, output digitally.

- 2. Analog quantities:

- a. vary smoothly, then change abruptly to new values.

- b. consist of codes of high-level and low-level signals.

- c. vary smoothly continuously.

- d. have periods of high-level and low-level signals, then change to continuous signals.

- 3. Digital signals:

- a. vary smoothly, then change abruptly to new values.

- b. consist of codes of high-level and low-level signals.

- c. vary smoothly continuously.

- d. have periods of high-level and low-level signals, then change to continuous signals.

- 4. Electronic system designers must interface between:

- a. the human world and the electronic world.

- b. the wholesale world and the retail world.

- c. the private business world and the government business world.

- d. the analog world and the digital world.

- e. a and d above.

- f. none of the above.

- 5. In analog electronic systems, analog quantities are:

- a. not analogous to the original quantity.

- b. are not a copy of the original quantity in another form.

- c. are output in digital form.

- d. are a copy of the analog physical quantity in another form.

- 6. Binary digital systems:

- a. have two discrete levels—1 or 0, high level or low level.

- b. have three or more discrete levels.

- c. have a level that varies continuously with time.

- d. have binary digits, or bits for short.

- e. none of the above.

- f. d and a above.

- 7. Decimal numbering systems have:

- a. weighted digit positions that vary randomly.

- b. weighted digit positions varying by powers of 10.

- c. weighted digit positions varying by powers of 2.

- d. weighted digit positions that remain constant at one value.

- 8. Decimal numbering systems have:

- a. weighted digit positions that vary randomly.

- b. weighted digit positions varying by powers of 10.

- c. weighted digit positions varying by powers of 2.

- d. weighted digit positions that remain constant at one value.

- 9. Physical quantities in the human world are typically:

- a. digital and analog.

- b. analog and digital.

- c. digital.

- d. analog.

- 10. Digital systems represent quantities:

- a. using combinations of binary digits in codes.

- b. using more bits in its binary codes as the quantity value increases.

- c. using more bits in its binary code as more accuracy is required.

- d. using binary codes with just two levels -1 or 0, high level or low level.

- e. none of the above.

- f. all of the above.

#### 11. Analog quantities:

- a. usually have slow response and less than high accuracy.

- b. can be maintained at very high accuracy at very high computing speeds.

- c. are impossible to compute.

- d. either have slow response or very high accuracy.

#### 12. Digital quantities:

- a. usually have slow response and less than high accuracy.

- b. can be maintained at very high accuracy at very high computing speeds.

- c. are impossible to compute.

- d. either have slow response or very high accuracy.

- 13. The basic functions for A-to-D (analog-to-digital) conversions are:

- a. Sense, compute digitally, convert to analog.

- b. compute as analog, sense, convert to digital.

- c. convert to digital, sense, condition to analog.

- d. sense, condition, convert to digital.

#### 14. Sensing:

- a. computes analog quantities in nature.

- b. separates out analog quantities into different categories.

- c. changes quantities in nature to electrical signals.

- d. detects analog quantities by their magnitude.

#### 15. Conditioning signals:

- a. means that the signals are being exercised.

- b. means that some characteristic of the signal is being changed.

- means that the input signal may be increased or decreased in amplitude, filtered or its impedance changed.

- d. means that nothing is done to the input signal.

- e. b and c above.

- f. a and d above.

## Signal Paths from Digital to Analog

#### Introduction

Refer back to *Figure 1-7*. In *Chapter 1*, the basic functions used for the analog-to-digital portion of *Figure 1-7* were discussed. In this chapter, the basic functions of the digital-to-analog portion will be discussed.

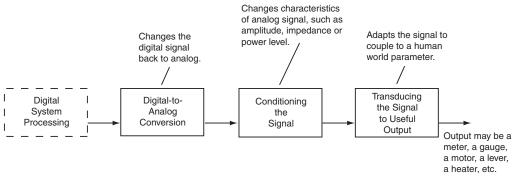

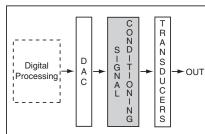

#### The Digital-to-Analog Portion

The digital-to-analog portion is separated out from *Figure 1-7* in *Figure 2-1*. After the digital processing system completes its manipulation of the signal, the output digital codes are coupled to a digital-to-analog converter that changes the digital codes back to an equivalent analog signal. From the output of the digital-to-analog converter, the analog signal is coupled to a signal conditioner that changes the characteristics of the signal. Just as in *Chapter 1*, as the application demands, the amplitude of the signal may be increased with amplification, or decreased with attenuation. Or maybe the power level of the signal is changed, or there may be an impedance transformation to fit the transducer to which the output signal couples.

The output of the system is to some real-world quantity external to the electronic system. As shown in *Figure 2-1*, the output might be a meter, a gauge, a motor, a lever arm to produce motion, a heater, or other similar output.

Figure 2-1: Digital-to-analog portion of the signal chain

#### Digital-to-Analog Conversion

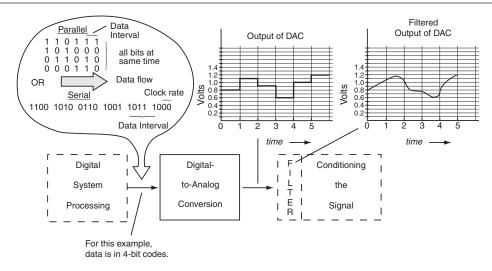

Figure 2-2 illustrates the basic digital-to-analog function. The digital processing system outputs digital information in the form of digital codes, and as shown, the digital codes are usually presented to the input of the digital-to-analog converter in one of two ways.

#### Parallel Transfer of Data

The first way—parallel bit transfer—means that all bits of the digital code are outputted at the same time. In *Figure 2-2*, a 4-bit code is used as an example. The 4-bit codes are coupled out in sequence as they are processed by the digital processor. They arrive at a preset data interval. In *Figure 2-2*, the 4-bit code 1000 is outputted first, followed by 1011, 1001, 0110, 1010, and 1100, respectively. The digital-to-analog converter

Figure 2-2: The basic function of digital-to-analog conversion

accepts all bits at the same time. It must have four input lines, the same number of input lines as the 4-bit code. In most modern day digital-to-analog converters the 4-bit codes of *Figure 2-2* are really 8-bit, or most likely 16-bit codes.

#### Example 1. Parallel Output

Refer to *Figure 2-2*. If the output of the digital-to-analog converter were an 8-bit code, what would the parallel bit codes be that are coupled out in sequence. Use the same value of analog signal.

#### Solution:

The analog values and the 4-bit codes are listed first. Since an 8-bit code can represent 256 segments, its codes for the same analog value are shown with the maximum analog signal of 1.5V equal to 255. Notice that the 8-bit code is two groups of 4-bit codes, which are also expressed in hexadecimal form.

| Analog value | 4-bit code | Hex | 8-bit | code | Hex |

|--------------|------------|-----|-------|------|-----|

| 0            | 0000       | 0   | 0000  | 0000 | 00  |

| 0.1          | 0001       | 1   | 0001  | 0001 | 11  |

| 0.2          | 0010       | 2   | 0010  | 0010 | 22  |

| 0.3          | 0011       | 3   | 0011  | 0011 | 33  |

| 0.4          | 0100       | 4   | 0100  | 0100 | 44  |

| 0.5          | 0101       | 5   | 0101  | 0101 | 55  |

| 0.6          | 0110       | 6   | 0110  | 0110 | 66  |

| 0.7          | 0111       | 7   | 0111  | 0111 | 77  |

| 0.8          | 1000       | 8   | 1000  | 1000 | 88  |

| 0.9          | 1001       | 9   | 1001  | 1001 | 99  |

| 1.0          | 1010       | A   | 1010  | 1010 | AA  |

| 1.1          | 1011       | В   | 1011  | 1011 | BB  |

| 1.2          | 1100       | C   | 1100  | 1100 | CC  |

| 1.3          | 1101       | D   | 1101  | 1101 | DD  |

| 1.4          | 1110       | Е   | 1110  | 1110 | EE  |

| 1.5          | 1111       | F   | 1111  | 1111 | FF  |

|              |            |     |       |      |     |

#### Serial Transfer of Data

The second way is serial transfer of data. As shown in *Figure 2-2*, the 4-bit codes are outputted one bit at a time, each following the other in sequence, and each group of four bits following each other in sequence. A clock rate determines the rate at which the bits are transferred. The digital-to-analog converter accepts the bits in sequence and reassembles them into the respective bit groups and then acts on them.

#### Example 2. Bit Rate

Refer to *Figure 2-2*. If the clock that outputs the bits in a serial output is 1 MHz, what are the serial bit transfer rate and the parallel bit transfer rate for a 4-bit and an 8-bit code?

#### Solution:

| Clock (Hz) | Serial |       | Parallel |       |

|------------|--------|-------|----------|-------|

|            | 4-bit  | 8-bit | 4-bit    | 8-bit |

| 1 MHz      | 1 MHz  | 1 MHz | 4 MHz    | 8 MHz |

#### The Conversion

The digital codes received by the digital-to-analog converter are equivalent to a particular analog value. As shown in *Figure 2-2*, the input code is converted to and outputted as the equivalent analog value and held as this value until the next code equivalent value is outputted. Thus, as shown, the output of the digital-to-analog converter is a stair-step output that stays constant at a particular level until the next input digital code is received. The output resembles an analog signal but further processing is required in order to arrive at the final analog signal.

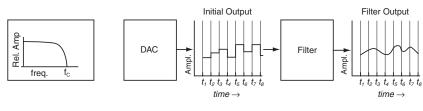

#### **Filtering**

A basic function required after the digital-to-analog conversion is filtering, or in more general terms, smoothing. As shown in *Figure 2-2*, such filtering produces an analog signal more equivalent to an analog signal that changes smoothly and continuously. The filter physically may be in the digital-to-analog converter or in the signal conditioner that follows it as shown in *Figure 2-2*. It was placed in the signal conditioner in *Figure 2-2* because it really is a signal conditioning function.

#### Conditioning the Signal

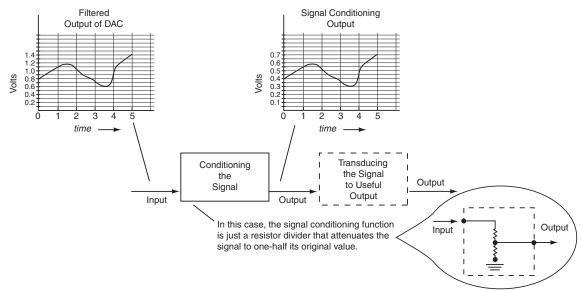

The function of conditioning the signal for the digital-to-analog portion can be the same as for the analog-to-digital portion. A most common function is amplification of the signal, but in like fashion, there is often the need to attenuate the signal; that is, to reduce the amplitude instead of increasing the amplitude. That is the function chosen for *Figure 2-3*. The output signal is attenuated to one-half the value of the input. No other characteristics of the signal are changed. The shape of the amplitude variations of the waveform with time are not changed, so the signal appears the same except its amplitude values are reduced.

#### Transducing the Signal

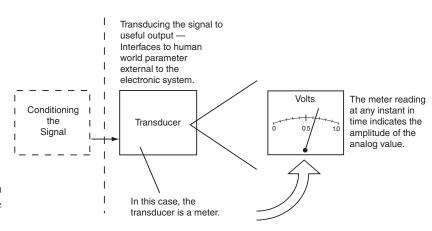

The output of the analog systems discussed is a human world parameter external to the electronic system. As mentioned previously several times, it may be a temperature, or a pressure, or a measure of humidity, or a linear motion, or a rotation. Thus, the electronic output of the signal conditioning function, in many cases, must be changed in form. It may be a voltage or a current out of the electronic system and must be changed to another form of energy.

A device to change or convert energy from one form to another is called a transducer. In *Figure 2-4*, the transducer is a meter that shows the amplitude of the output voltage on a voltage scale. The voltage output from the electronic system is converted to the rotation of a needle in front of a scale marked on the material

Figure 2-3: Signal conditioning function

behind the needle. The scale is calibrated so particular needle deflections represent specific voltage values. Thus, any deflection of the needle as a result of the electronic circuit output can be read as a particular voltage value at any instant of time. The electronic system output has been converted to a meter reading,

and the meter reading can be calibrated into the type of parameter the system is measuring. It could be a fluid level, a rate of flow, a pressure, and so forth.

Similar changes in energy form occur in other types of transducers. The voltage or current output from the electronic system gets converted to all forms of human world parameters just by the choice of the transducer.

#### **Examples of Transducers**

Figure 2-4: The transducer function

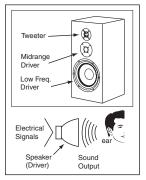

Figure 2-5 shows examples

of various types of transducers. *Figure 2-5a* is a picture of a speaker enclosure. Inside is what is called a driver. It is a common transducer that takes electrical audio signals and converts them into sound waves. The driver is placed inside a box to make it into a very good sounding speaker enclosure. Many times the driver only handles the low and mid-frequency audio signals, so another driver for the high frequencies, called a tweeter, is inserted into the speaker enclosure to allow the speaker to reproduce a broader range of audio frequencies.

a. Audio speaker

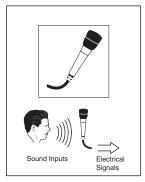

b. Microphone (sensor)

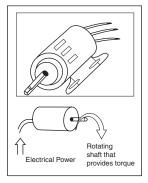

c. Motor

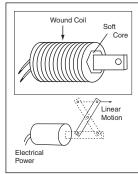

d. Solenoid

Figure 2-5: Examples of transducers

There is a counterpart transducer to the speaker—a microphone—that is used as an input device for sensing the signal. It is shown in *Figure 2-5b*. The microphone converts sound signals into electrical signals so they may be inputted into an electronic system.

Figure 2-5c shows a motor. Normally a motor is not classified as a transducer, but it is. A motor takes electrical energy and converts it into rotational torque. Motors are used everywhere, from running machinery, to trimming grass, to providing transportation.

Figure 2-5d shows a solenoid. A solenoid is a transducer that converts electrical energy into linear motion. It consists of a coil of wire with a soft iron core inside of it. When current is passed through the coil, a magnetic field is produced that pulls on the soft iron core and draws it inside the core. The movement of the core can be used to move a lever arm, to close a door, to operate a shutter, and so forth.

There are many more examples of transducers that convert electrical energy into a pressure, a valve for controlling fluid flow, a temperature gauge, and so forth. As various applications are described in subsequent chapters many will use various types of transducers.

#### Summary

The discussion in this chapter covered the functions necessary to convert a digital signal into an analog output and then into a human world parameter. It completed the signal chain from an input analog signal, to a digital conversion, to computation in digital form, to a conversion back to an output analog signal, to an output human world parameter. The next chapter will examine the sensing function in detail.

#### Chapter 2 Quiz

- 1. A digital-to-analog converter:

- a. outputs a digital signal in serial form.

- b. outputs an analog signal in stair-step form.

- c. outputs a smooth and continuous analog signal.

- d. outputs one digital code after another.

- 2. The output of the digital-to-analog chain is:

- a. a serial digital code string.

- b. a parallel digital code stream.

- c. a real-world quantity.

- d. always a meter reading.

- 3. An input to a digital-to-analog converter may be:

- a. a parallel transfer of digital codes.

- b. an analog signal of suitable amplitude.

- c. an analog signal of discrete values.

- d. a serial transfer of digital codes.

- e. a and d above.

- f. b and c above.

- 4. In a parallel transfer of bits:

- a. all bits of a digital code are transferred at the same time.

- b. all bits of a digital code are transferred in a sequential string.

- c. all bits are filtered into an analog signal.

- d. all bits are signal conditioned one at a time.

- 5. In a serial transfer of bits:

- a. all bits of a digital code are transferred at the same time.

- b. all bits of a digital code are transferred in a sequential string.

- c. all bits are filtered into an analog signal.

- d. all bits are signal conditioned one at a time.

- 6. The output of the digital-to-analog converter is:

- a. a stair-step output that varies until the next input digital code is received.

- a stair-step output that changes between 1 and 0 until the next digital code is received.

- c. a stair-step output that stays constant at a particular level until the next digital code is received.

- a stair-step output that changes from maximum to minimum until the next digital code is received.

- 7. The digital-to-analog output must be filtered to:

- a. clarify the digital steps in the output.

- b. keep the stair-step digital output.

- c. make the analog output change smoothly and continuously.

- d. make the analog output more like a digital output.

- 8. A transducer is:

- a. a device to change or convert energy from one form to another.

- b. a device that maintains the analog output in digital steps.

- c. a device that converts analog signals to digital signals.

- d. a device that converts digital signals to analog signals.

#### 9. A motor is:

- a. a transducer that changes digital signals into analog signals.

- b. a transducer that changes analog signals into digital signals.

- c. a transducer that raises the analog voltage output to a higher voltage.

- d. a transducer that changes electrical energy into rotational torque.

#### 10. A meter is:

- a. a transducer that converts the analog output to the rotation of a needle in front of a scale.

- b. a transducer that changes analog signals into digital signals.

- c. a transducer that raises the analog voltage output to a higher voltage.

- d. a transducer that changes digital signals into analog signals.

Answers: 1.b, 2.c, 3.e, 4.a, 5.b, 6.c, 7.c, 8.a, 9.d, 10.a.

### Sensors

#### Introduction

In *Chapter 1*, *Figure 1-8* shows the basic functions needed when going from an analog quantity to a digital output. The first of these is sensing the analog quantity. The device used in the function to sense the input quantity and convert it to an electrical signal is called a *sensor*—the main subject of this chapter.

A sensor is a device that detects and converts a natural physical quantity into outputs that humans can interpret. Examples of outputs are meter readings, light outputs, linear motions and temperature variations. *Chapter 1* indicated that a majority of these physical quantities are analog quantities; i.e., they vary smoothly and continuously. Sensors, in their simplest form, are devices that contain only a single element that does the necessary transformation. Although today, more and more complicated sensors are being manufactured; they cover more than the basic function, containing sensing, signal conditioning and converting all in one package.

In this chapter, in order to clearly communicate the sensing function, the majority of sensors will be single element sensors that output electrical signals—voltage, current or resistance. But also, closely coupled to sensors with electrical outputs, sensors are included that use magnetic fields for their operation.

#### **Temperature Sensors**

#### **Oral Temperature**

Everyone, sometime or another, has had the need to find out their body temperature or the body temperature of a member of their family. An oral thermometer like the one shown in *Figure 3-1* was probably used. Liquid mercury inside of a glass tube expands and pushes up the scale on the tube as temperature increases. The scale is calibrated in degrees (°F—Fahrenheit in this case) of body temperature; therefore, the oral thermometer converts the physical quantity of temperature into a scale value that humans can read. The oral thermometer is a temperature

sensor with a mechanical scale readout.

Figure 3-2: Rear-view of bimetal strip thermometer

#### Indoor/Outdoor Thermometer

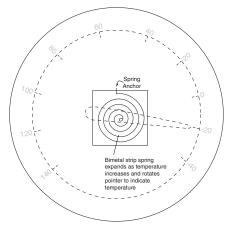

Another temperature sensor is shown in *Figure 3-2*. It is a bimetal strip thermometer. Two dissimilar metals are bonded together in a strip that is formed into a spring. The metals expand differently with temperature; therefore, a force is exerted between them that expands the spring and rotates the needle as the temperature increases. The thermometer scale is calibrated to known temperatures—boiling water and freezing water. These points establish a scale and the device is made into a commercial thermometer with Fahrenheit (°F) and/or Celsius (Centigrade—°C) scales. The one shown in *Figure 3-2* is for °F. The outdoor thermometer is another type of temperature sensor that converts the physical quantity of temperature into a meter reading easy for humans to see and interpret.

#### **Thermocouples**

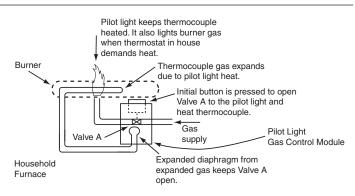

A thermocouple is another common temperature sensor. A place to find one is in a natural gas furnace in a home similar to that shown in *Figure 3-3*. It controls the pilot light for the burners in the furnace. The thermocouple is a closed tube system that contains a gas. The gas expands as it is heated and expands a diaphragm at the end of the tube that is in the gas control module.

The system works as follows: A button on the pilot light gas control module is

Figure 3-3: A residential furnace pilot light control

pressed to open valve A to initially allow gas to flow to light the pilot light. The expanded diaphragm of the thermocouple system controls valve A; therefore, the button for the pilot light must be held until the thermocouple is heated by the pilot light so that the gas expands and expands the diaphragm. The expanded diaphragm holds valve A open; therefore, the pilot light button can be released because the pilot light heating the thermocouple keeps the gas expanded. Since the pilot light is burning, any demand for heat from the thermostat will light the burners and the house is heated until the demand by the thermostat is met.

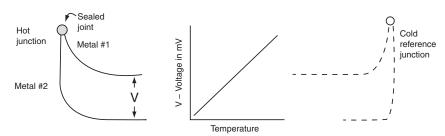

A thermocouple that puts out an electrical signal as temperature varies is shown in *Figure 3-4*. It is constructed by joining two dissimilar metals. When the junction of the two metals is heated, it generates a voltage, and the result is a temperature

Figure 3-4: A bimetal thermocouple

sensor that generates millivolts of electrical signal directly. The total circuit really includes a cold-junction reference, but the application uses the earth connection of the package as the cold reference junction.

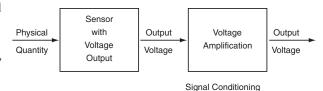

There may be a need to amplify the output signal from the sensor, as shown in *Figure 3-5*, because the output voltage amplitude must be increased to a useful level. This is the subject of *Chapter 4*, signal conditioning.

#### Silicon-Junction Diode

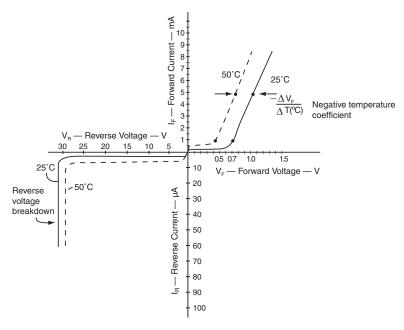

Another sensor that produces a voltage directly as temperature varies is a silicon-junction diode.

Figure 3-5: A sensor output signal may have to be increased to a useful level by amplification

The characteristic curves for its forward and reverse voltage with current are shown in *Figure 3-6*. The forward current versus forward voltage for positive voltages increases little until the forward voltage reaches +0.7V, then it increases rapidly. Here the forward resistance is very small—in the order of 50  $\Omega$  to 80  $\Omega$ .

The reverse current for negative reverse voltage is 1,000 times and more smaller than the forward current. It stays relatively flat with reverse voltage until the magnitude reaches the reverse breakdown voltage. When

the junction is reversed biased below the breakdown voltage, the reverse resistance is very large—in the order of megohms. The forward voltage and reverse breakdown voltage decrease as temperature is increased: thus, the diode junction has a negative temperature coefficient. The forward voltage has a much smaller voltage variation with temperature than does the reverse breakdown voltage. The reverse current below the breakdown region can also be used for a temperature sensor. A rule of thumb for the reverse current is that it doubles for every 10°C rise in temperature. The reverse conditions are used for temperature sensors, but the most common is to use the forward voltage change.

Figure 3-6: Silicon P-N junction characteristics

#### Example 1. Temperature Coefficient

Using Figure 3-6, calculate the temperature coefficient of the forward voltage of the diode and show that it is negative. The forward current  $I_F = 5$  mA.

#### Solution:

| T °C          | $V_{\mathrm{F}}$ |

|---------------|------------------|

| 25            | 1.02V            |

| <u>50</u>     | <u>0.70V</u>     |

| $\Delta = 25$ | -0.32V           |

Temp Coefficient =  $\Delta V_F/\Delta T = -0.32V/25^{\circ}C = -0.0128V/^{\circ}C$

#### **Thermistor**

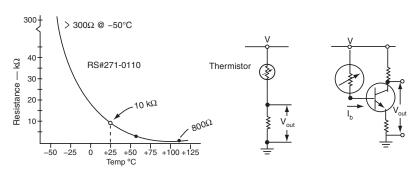

A thermistor is a resistor whose value varies with temperature. Figure 3-7a shows the characteristics of a thermistor readily available at RadioShack. Two circuits for the use of thermistors are shown in Figure 3-7. Figure 3-7b uses the thermistor in a voltage divider to produce a varying voltage output. Figure 3-7c uses a transistor to amplify the current change provided by the thermistor as

a. Characteristics

b. Voltage ouput c. Current output

Figure 3-7: Thermistor temperature sensor TEAM LRN 20

temperature changes. In some micromachined thermistors, the resistance at 25°C is of the order of  $10 \text{ k}\Omega$ . One of the disadvantages of using a thermistor is that its characteristics with temperature are not linear. As a result, in order to produce linear outputs, the nonlinearity must be compensated for.

#### **Angular and Linear Position**

#### Position Sensor—Fuel Level

In Chapter 1, Figure 1-2, an automobile fuel gauge was used to demonstrate an analog quantity. That same example will be used, as shown in Figure 3-8a, to demonstrate the sensing function. The complete sensor consists of a float that rides on the surface of fuel in a fuel tank, a lever arm connected to the float at one end, and, at the other end, connected to the shaft of a potentiometer (variable resistor). As the fuel level changes, the float moves and rotates the variable contact on the potentiometer. The schematic of Figure 3-8b shows that the potentiometer is connected across the automobile battery from +12V to ground. The variable contact on the potentiometer moves in a proportional manner. When the contact is at the end of the potentiometer that is connected to ground, the output voltage will be zero volts from the variable contact to ground. At the other end, the one connected to +12V, there will be +12V from the variable contact to ground. For any position of the variable contact in between the end points, the voltage from the variable contact to ground will be proportional to the amount of the shaft rotation.

Calibrating it as shown in *Figure 3-8c* completes the liquid-level sensor. At a full tank, the float, lever arm and potentiometer shaft rotation are designed so that the variable contact is at the +12V end of the potentiometer. When the tank is empty, the same combination of elements results in the variable contact at the ground level (0V). Other positions of the float result in proportional output voltages between the variable contact and ground. *As Figure 3-8c* shows, a three-quarter full tank gives an output of 9V, a half-full tank will give an output of 6V, and a one-quarter full tank will give an output of 3V. Thus, adding a voltmeter to measure the voltage from the variable contact to ground, marked in liquid level, completes the automotive fuel gauge. Sensors that convert a physical quantity into an electrical voltage output are very common. The output voltage can be anywhere from microvolts to tens of volts.

Figure 3-8: Position sensor—fuel level gauge TEAM LRN 21

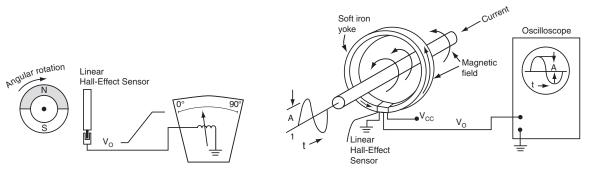

#### Hall Effect-Position Sensor

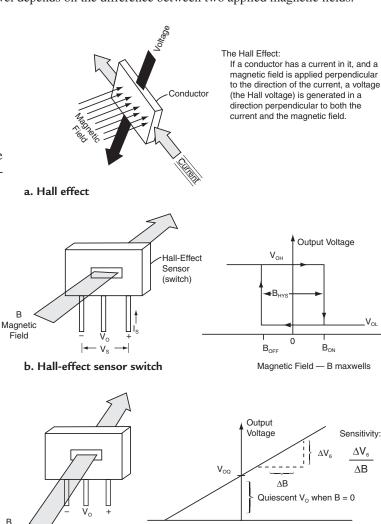

The Hall effect is shown in *Figure 3-9a*. E.H. Hall discovered it. If there is current in a conductor and a magnetic field is applied perpendicular to the direction of the current, a voltage will be generated in the conductor that has a direction perpendicular to both the direction of the current and the direction of the magnetic field. This property is very useful in making sensors, especially when a semiconductor chip is used for the conductor. Not only can the semiconductor be used to generate the Hall voltage, but additional circuitry can be built into the semiconductor to process the Hall voltage. As a result, not only are there linear sensors that generate an output voltage that is proportional to the magnitude of the magnetic flux applied, but, because circuitry can be added to the chip, there are sensors that have switched logic-level outputs, or latched outputs, or outputs whose level depends on the difference between two applied magnetic fields.

#### Hall Effect-Switch

Figure 3-9b shows a Hall-effect switch and its output when used as a sensor. When the magnetic flux exceeds  $\beta_{ON}$  in maxwells, the output transistor of the switch is ON, and when the field is less than  $\beta_{OFF}$ , the output transistor is OFF. There is a hysteresis curve as shown. When the output transistor is OFF, the magnetic field must be greater than zero by  $\beta_{ON}$  before the transistor is ON, but will stay ON until the magnetic field is less than zero by B<sub>OFF</sub> The zero magnetic field point can be "biased" up to a particular value by applying a steady field to make  $\beta_0 = B_{\text{STEADY-STATE}}$ .

#### Hall Effect-Linear Position

A linear Hall-effect sensor is shown in *Figure 3-9c*. Its output voltage varies linearly as the magnetic field varies. When the field is zero, there is a quiescent voltage =  $V_{OQ}$ . If the field is + $\beta$  (north to south), the voltage  $V_{O}$  increases from  $V_{OQ}$ ; if the field is - $\beta$  (south to north), the voltage  $V_{O}$  decreases from  $V_{OQ}$ . The supply voltage is typically 3.8V to 24V for Hall-effect devices.

c. Linear Hall-effect sensor

Magnetic

Field

Figure 3-9: Hall-effect sensors TEAM LRN 22

– B

+B

#### Hall Effect—Brake Pedal Position

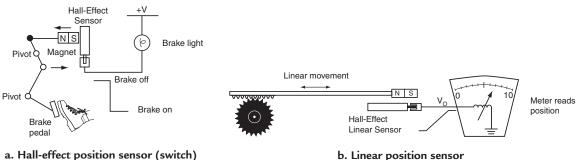

A brake pedal position sensor is shown in Figure 3-10a. A Hall-effect switching sensor is used. Stepping on the brake moves a magnet away from the Hall-effect sensor and its output switches to a low voltage level turning on the brake light. When the brake is released, the magnetic field is again strong enough to switch the output V<sub>0</sub> to a high level, turning off the brake light.

#### Hall Effect—Linear Position Sensor

In Figure 3-10b, as the magnet is moved over the sensor the magnetic field produces an output V<sub>0</sub> that is proportional to the strength of the field. The linear output voltage can be converted to a meter reading that indicates the linear position of the assembly that moves the magnet. Amplifying  $V_0$  can increase the sensitivity of the measurement.

## Hall Effect-Angular Position Sensor

A round magnet, half North pole and half South pole, is rotated in front of a linear Hall-effect sensor as shown in Figure 3-10c. As the magnet turns the magnetic field varies and produces an output V<sub>0</sub> that is proportional to the angular rotation.  $V_0$  can be converted to a meter reading calibrated in degrees of rotation.

#### Hall Effect—Current Sensor

Current in a wire produces a magnetic field around the wire as shown in *Figure 3-10d*. If the wire is passed through a soft-iron yoke, the soft iron collects the magnetic field and directs it to a linear Hall-effect sensor. The magnetic field varies as the amplitude of the current varies, which produces a corresponding proportional V<sub>O</sub> from the linear sensor, and, thus, a sensor that detects the amplitude of the current. An alternating current is shown in Figure 3-10d; therefore, the voltage V<sub>0</sub> will be an alternating voltage. V<sub>0</sub> is detected in Figure 3-10d using an oscilloscope.

c. Angular position sensor

d. Current sensor

Figure 3-10: Hall-effect sensor applications TEAM LRN 23

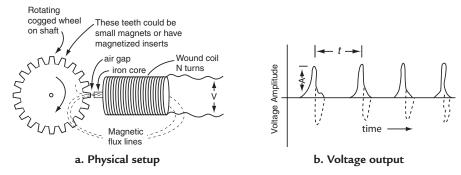

#### Rotation

#### Variable Reluctance Sensor

Figure 3-11a shows the physical setup of an electromagnetic sensor that produces a continuous series of voltage pulses as a result of time-varying changes of magnetic flux. The magnetic flux path in Figure 3-11a, called the reluctance path, is through the iron core of the wound coil, through the cog on the rotating wheel and back to the coil. When the cog on the wheel is aligned with the iron core, the concentration of flux is the greatest. As the cog moves toward or away from the core of the coil, the concentration of flux is much less. Anytime magnetic flux changes and cuts across wires, it generates a voltage in the wires. The voltage produces a current in the circuit attached to the wires. As a result of the rotation of the wheel and the cog past the coil, a series of voltage pulses, as shown in Figure 3-11b, is generated. The time, t, between the pulses varies as the speed of the cogged wheel varies. Counting the pulses over a set period of time, say, a second, the speed (velocity) of the cogged wheel can be calculated. The variations of the speed can be calculated for

acceleration, and of course, the presence of pulses means the wheel is in motion. The disadvantage of such a sensor is that there is no signal at zero speed, and the air gap between the mechanical moving part and the coil core must be small, usually equal to or less than 2–3 centimeters.

Figure 3-11: Variable reluctance rotation sensor

# Example 2. RPM

A variable reluctance sensor outputs 120 pulses in a time period of 3 seconds. What is the rpm (revolutions per minute)?

#### Solution:

rps (revolutions per sec) =  $120/3 = 40 \times 60$  sec = 2400 rpm

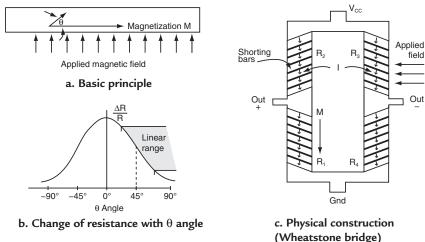

# Magnetoresistor Sensor

A magnetoresistor sensor changes its resistance proportional to the magnetic flux density to which it is exposed. It is made of a nickel-iron (Permalloy) which is deposited as a thin film onto a semiconductor surface. It requires special fabrication of conducting strips on high-carrier mobility semiconductors such as Indium-Antimonide or Indium Arsenide. The basic principle is shown *in Figure 3-12a*. The thin film is deposited in a strong magnetic field that orients the magnitization M in a direction parallel to the length of the resistor. A current is then made to pass through the thin film at an angle  $\theta$  to the M direction. If the angle is zero, the thin film will have the highest resistance. At an angle  $\theta$ , it will have a lower resistance. When an external magnetic field is applied perpendicular to M, then  $\theta$  changes and the resistance changes. This is the basic principle that produces a resistance change when a magnetic field is applied and allows the use of the thin film device as a sensor.

Figure 3-12b shows the change in resistance as the angle  $\theta$  of the current in relationship to M varies. One of the advantages of using magnetoresistor is that other semiconductor circuits can be fabricated on and in the same semiconductor substrate. The resistor element is usually placed in a Wheatstone bridge circuit in order to make a more sensitive measurement.

Such a physical layout is shown in *Figure 3-12c*.

Figure 3-12: Magnetoresistor sensor

There are shorting bars deposited over the film to direct the bias current at an angle equal to 45°. This is to put the quiescent point in *the* center of the linear region of operation of the response curve of *Figure 3-12b*. When  $V_{CC} = 5V$ , the bridge sensitivity can be as much as 15 mV per Oersted of an applied field.

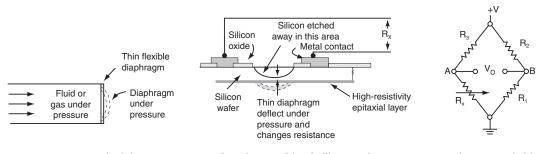

#### Pressure

# Piezoresistive Diaphragm

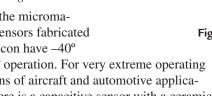

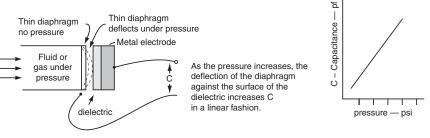

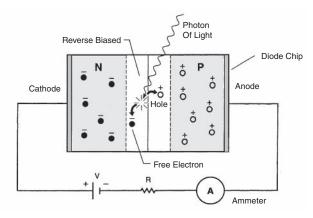

The physical construction of a pressure sensor is shown in *Figure 3-13a*. A fluid or gas under pressure is contained within a tube the end of which is covered with a thin, flexible diaphragm. As the pressure increases the diaphragm deflects. The deflection of the diaphragm can be calibrated to the pressure applied to complete the pressure sensor characteristics.